# Memristive State Equation for Bipolar Resistive Switching Devices Based on a Dynamic Balance Model and its Equivalent Circuit Representation

Enrique Miranda $^{1}$  and Jordi Suñé $^{2}$

<sup>1</sup>Universitat Autònoma de Barcelona <sup>2</sup>Affiliation not available

October 30, 2023

## Abstract

A memory state equation consistent with several experimental observations is presented and discussed within the framework of Chua's memristive systems theory. The proposed equation describes the evolution of the memory state corresponding to a bipolar resistive switching device subjected to a variety of electrical stimulus.

# Memristive State Equation for Bipolar Resistive Switching Devices Based on a Dynamic Balance Model and its Equivalent Circuit Representation

E. Miranda, IEEE Senior Member, J. Suñé, IEEE Fellow

Abstract— A memory state equation consistent with several experimental observations is presented and discussed within the framework of Chua's memristive systems theory. The proposed equation describes the evolution of the memory state corresponding to a bipolar resistive switching device subjected to a variety of electrical stimulus. It is shown that our approach is consistent with: i) the characteristic switching time associated with the ions/vacancies displacement within dielectric films, ii) the SET/RESET voltage dependence on the voltage sweep ramp rate, iii) the hysteretic nature of the memory state as a function of time and voltage for arbitrary input signals, iv) the generation of selfsimilar hysteron loops for different initial conditions, and v) the collapse of the memory window with the increment of the input signal frequency. It is also shown that the proposed equation admits a circuital representation suitable for circuit simulations.

Index Terms-memristor, resistive switching, memory

#### I. INTRODUCTION

central issue in L. Chua's memristive devices theory is A the definition of the memory state  $(\lambda - t)$  represented by a first order time differential equation [1]. This equation in combination with an expression for the current-voltage (I-V)characteristic describes the hysteretic behavior observed in many oxide-based resistive switching (RS) devices [2,3]. The memory equation (ME) relates to the nonvolatile system's conduction properties and is physically associated in the case of CBRAMs/OxRAMs with the metal ions/oxygen vacancies displacement (heavy particles flow) within the dielectric film caused by the application of an external electrical stimulus [4]. The I-V relationship describes the specific electron transport mechanism (light particles flow) considered in the conducting filament (CF). In general, the picture resembles cars (electrons) passing across a drawbridge (ions/vacancies) with variable load capacity ( $\lambda$ ). Since the first proposal of a memristive ME by Strukov et al. [5] many others followed [6-8]. The introduction of a window function in the ME acting as a boundary condition for  $\lambda$  represented a breakthrough in the modeling of the SET/RESET transitions but the approach was demonstrated to be not exempted of serious mathematical drawbacks [9,10]. Interestingly, even for nonlinear electron transport, the memory state  $\lambda$  is a measure of the device conductance in the lowvoltage region which contains all the information relevant to whole *I-V* curve [11,12]. However, beyond the many efforts carried out in the last decade, there is still no consensus on which ME better represents a wide spectrum of RS behaviors. Here, we explore up to what extend the ME can be simplified without sacrificing the constraints imposed by experiments. Of course, as happens with any other model, the elaboration of an analytic approach dismisses a large number of particularities which cannot be covered by a basic general framework. We show that the proposed model is consistent with several experimental observations for a variety of input signals including constant, ramped, pulsed and sinusoidal. To the best of our knowledge, this thorough analysis was not carried out before and demonstrates that simplicity, dimensional considerations, and symmetry arguments are essential ingredients for seting up a well-posed physical and mathematical model for RS devices.

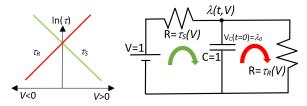

Fig.1: a) Schematic model for the SET (green) and RESET (red) characteristic switching times given by (2). b) Equivalent circuit model for the balance differential equation (1).  $\lambda$  is the memory state (voltage) and  $\lambda_0$  its initial value.

The central points of this new development are: first, we eliminate the so-called hysteron structure for the memory state as presented in [11,12]. Here, the proposed ME generates the hysteretic memory map by itself without *ad hoc* definitions. Second, we demonstrate through an in-depth analysis of its derivative that the proposed ME equation coinciliates both the static and dynamic switching conditions [2], and third, we show that the proposed ME not only has a compact recursive solution for the whole memory loop but also that it complies with Chua's observation regarding the collapse of the memory window with the signal frequency [1]. In addition, we show that the reported ME admits a simple equivalent circuit representation. This is of utmost importance for circuit simulations in which the timestep parameter is under the control of the simulator itself and not in hands of the user.

E. Miranda and J. Suñé are with the Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona (UAB), 08193 Barcelona, Spain (e-mail: enrique.miranda@uab.cat).

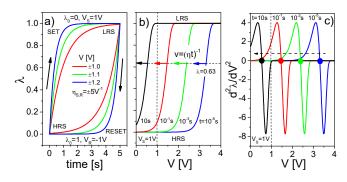

Fig.2: a) Potentiation and depression characteristics for constant voltage input, b) Evolution of the positive ridge function, c) Inflection point of  $\lambda(V)$ .

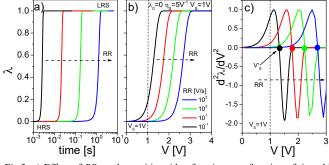

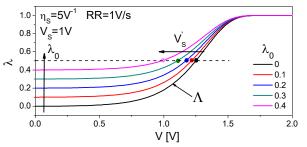

Fig.3: a) Effect of *RR* on the positive ridge function as a function of time, b) SET voltage shift, c) Evolution of the inflection point of  $\lambda(V)$  (normalized).

#### II. MEMORY STATE EQUATION AND CIRCUITAL APPROACH

The simplest first order time differential equation for  $\lambda$  satisfying dynamic balance, dimensional homogeneity, and long-term self-saturating behavior with end values 1 (LRS: low resistance state) and 0 (HRS: high resistance state) for opposite biases reads:

$$\frac{d\lambda}{dt} = \frac{1-\lambda}{\tau_S(\lambda, V)} - \frac{\lambda}{\tau_R(\lambda, V)}$$

(1)

where  $\tau_{S,R}$  [s] are characteristic times associated with the SET (V>0) and RESET (V<0) transients. We assume for  $\tau_{S,R}$  a voltage dependence of the form (see Fig.1.a):

$$\tau_{S,R}(V) = exp\left[-\eta_{S,R}\left(V - V_{S,R}\right)\right]$$

(2)

where  $\eta_{S,R}$  [V<sup>-1</sup>] and  $V_{S,R}$  [V] are the transition rates ( $\eta_S > 0$ ,  $\eta_R < 0$ ) and the reference switching voltages ( $V_S > 0$ ,  $V_R < 0$ ), respectively. Any dependence of  $\tau_{S,R}$  on  $\lambda$  in (2) requires the use of a circuit simulator. Notice that (2) is a convenient approximation since  $\tau_{S,R}(V=0)=\infty$  would be ideally expected (infinite retention time) [13]. In any case, for typical parameter values, the balance equation (1) yields  $d\lambda/dt(V=0)\approx 0$  as required for the equilibrium state. (1) has also been used in the past but in connection with physical parameters of the CF [14-17], not as a general memory state variable. Before solving (1) for some cases of particular interest, it is worth pointing out that its mathematical structure is that of an RC circuit with *V*-dependent resistors (see Fig.1.b). At the end, this will allow us to solve  $\lambda$  for arbitrary input signals.  $\lambda$  corresponds to the voltage drop across the capacitor C=1F (this is not a physical

capacitor) with initial voltage  $\lambda_0$ . This representation replaces the *V*-controlled memory subcircuits considered in many memristor models [10].

#### III. MODEL RESULTS AND ANALYSIS

Let us focus now on some relevant analytic results for the SET transition (V>0). Corresponding results for RESET (V<0) can be obtained *mutatis mutandis*.

i) Memory state evolution under constant voltage input signal

Neglecting the second term in the right-hand side of (1) and considering a constant voltage V>0 applied across the device, we find:

$$\lambda(t,V) = (\lambda_0 - 1)exp\{-t/\tau_S(V)\} + 1 \tag{3}$$

which has attractor 1 as  $t \rightarrow \infty$  regardless of  $\lambda_0$  and  $\tau_s$ . As shown in Fig.2.a, (3) and its counterpart for V < 0 (not shown here), describe the typical potentiation/depression effect in a synaptic cell [18]. If we identify the SET time  $\tau'_s$  with the inflection point of (3) as a function of V,  $d^2\lambda/dV^2=0$ , we obtain:

$$\tau'_{S}(V) = exp[-\eta_{S}(V - V_{S})] = \tau_{0}exp(-V/V_{0})$$

(4)

which coincides with the original expression (2) corresponding to the voltage-acceleration law for metal ions/oxygen vacancies displacement [19-23]. As illustrated in Figs.2.b and 2.c, this can be alternatively visualized as the time required by the point  $\lambda = (\lambda_0 - I)exp(-1)+1$  ( $\lambda = 0.63$  for  $\lambda_0 = 0$ ) in the travelling ridge function to reach the SET voltage condition (vertical dashed line). Within this picture, the inflection point moves towards the left with non-uniform velocity  $v = (\eta t)^{-1}$  [Vs<sup>-1</sup>].  $\tau_0 = exp(\eta_S V_S)$  [s] and  $V_0 = 1/\eta_S$  [V] in (4) are constants of the model and can be found experimentally [24].

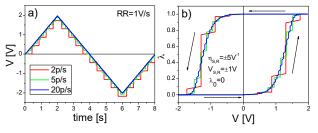

Fig.4: a) Pulsed signals with different number of pulses per second, b) Hysteron structure generated as a function of the applied bias using (7).

*ii) Memory state evolution under a linear voltage sweep*

Now, if we let  $V=RR \cdot t$ , with RR > 0 [Vs<sup>-1</sup>] the ramp rate, (1) can be integrated in terms of V>0 (see Figs. 3.a and 3.b):

$$\lambda(V) = (\lambda_0 - 1)exp\left\{-\frac{V_0}{\tau_0 RR}\left[exp\left(\frac{V}{V_0}\right) - 1\right]\right\} + 1 \quad (5)$$

As in *i*), the SET voltage  $V'_S$  corresponds to the condition  $d^2 \lambda / dV^2 = 0$  (Fig. 3.c), yielding:

$$V_{S}' = V_0 \ln(RR) + V_0 ln\left(\frac{\tau_0}{V_0}\right) \tag{6}$$

which expresses the well-known  $V_S$ -ln(*RR*) linear relationship [4,25-28]. Remarkably, (6) provides the link between the dynamical and static switching condition case given by (4).

#### iii) Hysteretic behavior for arbitrary input signals

In the case of an arbitrary input signal V(t) (positive or negative, continuous or discontinuous, derivable or not), (3) can be discretized following the recursive scheme:

$$\lambda_{t+1} = [\lambda_t - H(V_t)]exp\{-\Delta t/\tau_{S,R}(V_t)\} + H(V_t)$$

(7)

where  $\Delta t$  is the timestep considered between the states *t* and *t*+1,  $V_t$  the voltage applied during this time, and H(x) the Heaviside function. Notice that (7) is suitable for dealing with excitations formed by train of pulses with varying amplitude and different pulse rates as illustrated in Figs. 4.a and 4.b. In the continuous limit, (7) naturally generates the sigmoidal hysteron structure  $\lambda$ -V (positive and negative ridge functions) introduced in [11,29,30]. In the present approach, this mathematical structure is no longer required.

Fig.5: Major and minor positive ridge functions. Symbols are the SET voltages as a function of the initial condition  $\lambda_0$ .

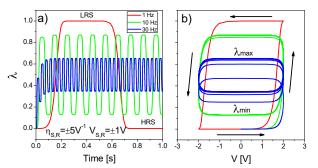

Fig.6: a) Evolution of  $\lambda$  for different input frequencies, b) Collapse of the memory window for a sinusoidal signal with fixed amplitude A=2V.

### iv) Self-similar loops and role played by the initial condition

As showed in [31], major (maximum voltage excursion) and minor (bounded voltage excursions) memory loops exhibit selfsimilar properties. The positive ridge function for the major loop  $\Lambda$  is obtained from (5) considering  $\lambda_0=0$ :

$$\Lambda(V) = 1 - exp\left\{-\frac{V_0}{\tau_0 RR}\left[exp\left(\frac{V}{V_0}\right) - 1\right]\right\}$$

(8)

Minor  $\lambda$  loops with arbitrary initial conditions (see Fig.5) can be expressed as affine transformations of  $\Lambda$  since:

$$\lambda(V) = (1 - \lambda_0)\Lambda(V) + \lambda_0 \tag{9}$$

In other words, this means that the properties found for the major loop propagate to the minor loops after appropriate scaling. If we adopt a definition for the SET condition based on the current magnitude ( $\lambda$ =0.5 for instance) instead of on the voltage, Fig. 5 reveals that  $V'_{S}$  reduces as  $\lambda_{0}$  increases. This indicates that more leaky devices switch on first [32].

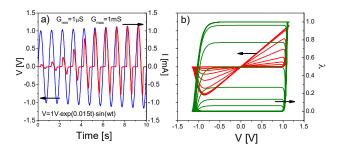

Fig.7: a) Effect of an increasing sinusoidal voltage (blue line) on the current (red) as a function of time. b) Corresponding evolution of the memory state (green) and generation of intermediate states in the I-V characteristic (red).

#### v) Memory window vs input signal frequency

A natural consequence of (6) is the collapse of the memory window (difference between  $\lambda_{max}$  and  $\lambda_{min}$  in the attractor curve) as the input signal frequency increases [1,33,34]. Figure 6 illustrates the effect of a sinusoidal voltage with constant amplitude A and frequency  $\omega$  on the hysteretic behavior of  $\lambda$ . These results were obtained using the circuit shown in Fig.1.b. From (6), it is clear that for any signal of amplitude A, ideally, one can always find a sufficiently large RR such that  $V'_S > A$ . This corresponds to a partial SET condition which limits the maximum excursion of  $\lambda$ . Physically, the collapse of the memory window is often attributed to the inability of ions/vacancies to follow the input signal [35,36]. This connection is theoretically demonstrated here using an experimentally validated voltage-acceleration law for the hopping time of the heavy particles, eq. (4).

#### IV. SIMULATION OF THE I-V CHARACTERISTIC

This final Section illustrates how the memory state  $\lambda$  is linked to a specific electron transport model. For the sake of simplicity, a linear *I-V* characteristic was chosen [5], but more complex behaviors are acceptable [12]. In this case:

$$I = [(1 - \lambda)G_{min} + \lambda G_{max}]V$$

(10)

where  $G_{min}$  and  $G_{max}$  [S] are the minimum and maximum conductance values, respectively, achievable without inducing irreversible damage to the device. These parameters are required to calibrate the model with the experimental HRS and LRS curves. Typical simulations results for *I*-*t* and *I*-*V* showing intermediate conduction states are depicted in Figs. 7.a and 7.b.

#### V. CONCLUSIONS

In this letter, a dynamic balance model for the memory equation of memristive devices exhibiting the bipolar resistive switching mode is proposed. The model complies with several experimental observations related to the switching voltages and times. Because of its simple mathematical structure, the model can be described in terms of an equivalent circuit with voltagedependent components. This property makes the proposed approach very useful for circuit simulation environments.

#### References

- L. Chua, "Resistance switching memories are memristors," Appl Phys A 102, 765-783 (2011). DOI: 10.1007/s00339-011-6264-9

- [2] E. Linn, A. Siemon, R. Waser, S. Menzel, "Applicability of wellestablished memristive models for simulations of resistive switching devices," IEEE Trans Cir Sys 61, 2402-2410 (2014). DOI: 10.1109/TCSI.2014.2332261

- [3] J. Blasco, N. Ghenzi, J. Suñé, P. Levy, E. Miranda, "Equivalent circuit modeling of the bistable conduction characteristics in electroformed thin dielectric films," Mic Rel 55, 1-14, (2015). DOI: 10.1016/j.microrel.2014.10.017

- [4] R. Waser, R. Dittmann, G. Saikov, K. Szot, "Redox-based resistive switching memories – Nanoionic mechanisms, prospects, and challenges," Adv Mater 21, 2632-2663 (2009). DOI: 10.1002/adma.200900375

- [5] D. Strukov, G. Snider, D. Stewart, R.S Williams, "The missing memristor found," Nature 453, 80-83 (2008). DOI: 10.1038/nature06932

- [6] P. Sheridan, K. Kim, S. Gaba, T. Chang, L. Chen, W. Lu, "Device and SPICE modeling of RRAM devices," Nanoscale 3, 3833-3840 (2011). DOI: 10.1039/c1nr10557d

- [7] J. Zha, H. Huang, T. Huang, J. Cao, A. Alsaedi, F. Alsaadi, "A general memristor model and its applications in programmable analog circuits," Neurocomputing 267, 134-140 (2017). DOI: 10.1016/j.neucom.2017.04.057

- [8] D. Panda, P. Sahu, T. Tseng, "A collective study on modeling and simulation of resistive random access memory," Nano Res Lett 13:8, (2018). DOI: 10.1186/s11671-017-2419-8

- [9] D. Biolek, Z. Biolek, V. Biokova, Z. Kolka, "Modeling of TiO<sub>2</sub> memristor: from analytic to numerical analysis," Semicond Sci Technol 29, 125008 (2014). DOI: 10.1088/0268-1242/29/12/125008

- [10] D. Biolek, Z. Biolek, V. Biokova, Z. Kolka, "Reliable modeling of ideal generic memristors via state-space transformation," Radioengineering 24, 393-407 (2015). DOI: 10.13164/re.2015.0393

- [11] E. Miranda, "Compact model for the major and minor hysteretic I-V loops in nonlinear memristive devices." IEEE Trans Nanotech 14 (2015). DOI: 787. 10.1109/TNANO.2015.2455235

- [12] G. Patterson, J. Suñé, E. Miranda, "Voltage-driven hysteresis model for resistive switching: SPICE modeling and circuit applications," IEEE Trans. Comp. Aided Des. Int. Circ. Sys. 36, 2044 (2017). DOI: 10.1109/TCAD.2017.2756561

- [13] A. Rodriguez-Fernandez, J. Muñoz-Gorriz, J. Suñé, E. Miranda, "A new method for estimating the conductive filament temperature in OxRAM devices based on escape rate theory," Mic Rel 88, 142-146 (2018). DOI: 10.1016/j.microrel.2018.06.120

- [14] M. Bocquet, D. Deleruyelle, H. Aziza, C. Muller, J. Portal, T. Cabout, E. Jalaguier, "Robust compact model for bipolar oxide-based resistive switching memories," IEEE Trans Elect Dev 61, 674-681 (2014). DOI: 10.1109/TED.2013.2296793

- [15] S. Blonskowski, T. Cabout, "Bipolar resistive switching from liquid helium to room temperature," J Phys D: Appl Phys 48, 345101 (2015). DOI: 10.1088/0022-3727/48/34/345101

- [16] G. González-Cordero, J.B. Roldan, F. Jiménez-Molinos, J. Suñé, S. Long, M. Liu, "A new compact model for bipolar RRAMs based on truncatedcone conductive filaments-a Verilog-A approach," Semicond Sci Technol 31, 115013 (2016). DOI: 10.1088/0268-1242/31/11/115013

- [17] Z. Wang, S. Ambrogio, S. Balatti, S. Sills, N. Ramaswamy, D. Ielmini, "Postcycling degradation in metal-oxide bipolar resistive switching memory," IEEE Trans Electron Dev 63, 4279-4287 (2016). DOI: 10.1109/TED.2016.2604370

- [18] C. Sung, H. Hwang, I. Yoo, "Perspective: A review on memristive hardware for neuromorphic computation," J Appl Phys 124, 151903 (2018). DOI: 10.1063/1.5037835

- [19] S. Menzel, S. Tappertzhofen, R. Waser, I. Valov, "Switching kinetics of electrochemical metallization memory cells," Phys Chem Phys 15, 6945 (2013). DOI: 10.1039/c3cp50738f

- [20] J. Yang, D. Strukov, D. Stewart, "Memristive devices for computing," Nature Nano 8, 13-24 (2013). DOI: 10.1038/NNANO.2012.240

- [21] J. Lee, S. Lee, T. Noh, "Resistive switching phenomena: A review of statistical physics approaches," Appl Phys Rev 2, 031303 (2015). DOI: 10.1063/1.4929512

- [22] F. Cuppers, S. Menzel, C. Bengel, A. Hardtdegen, M. von Witzleben, U. Bottger, R. Waser, S. Hoffmann-Eifert, "Exploiting the switching dynamics of HfO<sub>2</sub>-based ReRAM devices for reliabile analog memristive behavior," Appl Phys Mat 7, 091105 (2019). DOI: 10.1063/1.5108654

- [23] A. Mehonic, A. Shluger, D. Gao, I. Valov, E. Miranda, D. Ielmini, A. Bricalli, E. Ambrosi, C. Li, J. Yang, Q. Xia, A.J. Kenyon, "Silicon oxide (SiO<sub>x</sub>): A promising material for resistive switching?," Adv Mat 30, 1801187 (2018). DOI: 10.1002/adma.201801187

- [24] A. Rodriguez-Fernandez, C. Cagli, J. Suñé, E. Miranda, "Switching voltage and time statistics of filamentary conductive paths in HfO<sub>2</sub>-based ReRAM devices," IEEE Electron Dev Lett 39, 656-659, 2018. DOI: 10.1109/LED.2018.2822047

- [25] C. Cagli, F. Nardi, D. Ielmini, "Modeling of Set/Reset operations in NiObased resistive-switching memory devices," IEEE Trans Electron Dev 56, 1712-1720 (2009). DOI: 10.1109/TED.2009.2024046

- [26] S. Ambrogio, S. Balatti, D. Gilmer, D. Ielmini, "Analytical modeling of oxide-based bipolar resistive memories and complementary resistive switches," IEEE Trans Electron Dev 61, 2378-2386 (2014). DOI: 10.1109/TED.2014.2325531

- [27] P. Lorenzi, R. Rao, F. Irrera, "Role of the electrode metal, waveform geometry, temperature, and postdeposition treatment on SET and RESET of HfO<sub>2</sub>-based resistive random access memory 1R-cells: Experimental aspects," J Vac Sci Technol B 33, 01A107 (2015). DOI: 10.1116/1.4905426

- [28] A. Rodriguez-Fernandez, C. Cagli, L. Perniola, J. Suñé, and E. Miranda, "Effect of the voltage ramp rate on the set and reset voltages of ReRAM devices," Mic Eng 178, 61-65 (2017). DOI:10.1016/j.mee.2017.04.039.

- [29] M. Pedro, J. Martin-Martinez, R. Rodriguez, M.B. Gonzalez, F. Campabadal, M. Nafria, "A flexible characterization methodology of RRAM: Application to the modeling of the conductivity changes as synaptic weight updates," Solid St Electron 159, 57-62 (2019). DOI: 10.1016/j.sse.2019.03.035

- [30] S. Dueñas, H. Castán, H. García, O. Ossorio, L. Domínguez, E. Miranda, "Experimental observation of negative susceptance in HfO<sub>2</sub>-based RRAM devices," IEEE Electron Dev Lett 38, 1216-1219 (2017). DOI: 10.1109/LED.2017.2723054

- [31] H. Castán, S. Dueñas, H. García, O. Ossorio, L. Domínguez, B. Aahelices, E. Miranda, M.B. González, F. Campabadal, "Analysis and control of the intermediate memory states of RRAM devices by means of admittance parameters," J Appl Phys 124, 152101 (2018). DOI: 10.1063/1.5024836

- [32] D. Ielmini, "Brain-inspired computing with resistive switching memory (RRAM): Devices, synapses and neural networks," Mic Eng 190, 44-53 (2018). DOI: 10.1016/j.mee.2018.01.009

- [33] T. Dongale, K. Patil, P. Gaikwad, R. Kamat, "Investigating conduction mechanism and frequency dependency of nanostructured memristor device," Mat Sci Semic Proc 38, 228-233 (2015). DOI 10.1016/j.mssp.2015.04.033

- [34] J. Eshraghian, S. Kang, S. Baek, G. Orchard, H. Iu, W. Lei, "Analog weights in ReRAM DNN accelerators," IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2019. DOI: 10.1109/AICAS.2019.8771550

- [35] M. Sah, H. Kim, L. Chua, "Brains are made of memristors," IEEE Circuits and Systems Magazine, First Quarter 2014, 12-36 (2014). DOI: 10.1109/mcas.2013.2296414

- [36] K. Campbell, K. Drake, E. Barney Smith, "Pulse shape and timing dependence on the spike-timing dependent plasticity response of ionconducting memristors as synapses," Front Bioeng Biotechnol 4, 1-11 (2016). DOI: 10.3389/fbioe.2016.00097