# High-Density Memristor-CMOS Ternary Logic Family

Xiaoyuan Wang  $^1,$  Pengfei Zhou  $^1,$  Jason Eshraghian  $^2,$  Chih-Yang Lin  $^1,$  Herbert Ho-Ching Iu  $^1,$  Ting-Chang Chang  $^1,$  and Sung-Mo Kang  $^1$

October 30, 2023

#### Abstract

This paper presents the first experimental demonstration of a ternary memristor-CMOS logic family. We systematically design, simulate and experimentally verify the primitive

logic functions: the ternary AND, OR and NOT gates. These are then used to build combinational ternary NAND, NOR, XOR and XNOR gates, as well as data handling ternary MAX and MIN gates. Our simulations are performed using a 50-nm process which are verified with in-house fabricated indium-tin-oxide memristors, optimized for fast switching, high transconductance, and low current leakage. We obtain close to an order of magnitude improvement in data density over conventional CMOS logic, and a reduction of switching speed by a factor of 13 over prior state-of-the-art ternary memristor results. We anticipate extensions of this work can realize practical implementation where high data density is of critical importance.

<sup>&</sup>lt;sup>1</sup>Affiliation not available

<sup>&</sup>lt;sup>2</sup>University of Michigan

# High-Density Memristor-CMOS Ternary Logic Family

Xiaoyuan Wang, Pengfei Zhou, Jason K. Eshraghian, *Member, IEEE*, Chih-Yang Lin, Herbert H. C. Iu, *Senior Member, IEEE*, Ting-Chang Chang, and Sung-Mo Kang *Life Fellow, IEEE*

Abstract—This paper presents the first experimental demonstration of a ternary memristor-CMOS logic family. We systematically design, simulate and experimentally verify the primitive logic functions: the ternary AND, OR and NOT gates. These are then used to build combinational ternary NAND, NOR, XOR and XNOR gates, as well as data handling ternary MAX and MIN gates. Our simulations are performed using a 50-nm process which are verified with in-house fabricated indium-tin-oxide memristors, optimized for fast switching, high transconductance, and low current leakage. We obtain close to an order of magnitude improvement in data density over conventional CMOS logic, and a reduction of switching speed by a factor of 13 over prior state-of-the-art ternary memristor results. We anticipate extensions of this work can realize practical implementation where high data density is of critical importance.

Index Terms—logic, memristor, multilevel, RRAM, ternary.

# I. INTRODUCTION

ONVENTIONAL digital systems compute using binary logic, where only two possible values are available in the Boolean space. While this allows for large noise margins, there are applications where the need for data density is more critical. For example, commercial solid-state drives use quad level cells (QLC) for high storage density [1], [2], but come at the cost of slow write times. Various serial links, such as Gigabit Ethernet [3], employ similar multilevel techniques when the channel bandwidth is insufficient. Analog-to-digital converters also take advantage of ternary logic where redundancy is used to reduce quantization errors [4]–[6].

The design of ternary logic in VLSI-amenable implementations using MOSFETs dates back to the 1980s [7], and BJT design even further back to the 1960s [8]. Multilevel logic enables pre-processing multilevel cells (MLC) prior to binary expansion, and is one of many options for improving high-speed data density and channel bandwidth. But beyond data encoding and high-density storage class memory, multilevel logic has seen limited use. This is because ternary logic circuits require more gates than their CMOS counterparts,

- X. Wang and P. Zhou are with the School of Electronics and Information, Hangzhou Dianzi University, Hanzghou, 310018 China. (e-mail: youyuan-0213@163.com).

- J. K. Eshraghian is with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI, 48105 USA.

- C. Y. Lin and T.-C. Chang are with the Department of Physics, National Sun Yat-Sen University, Kaohsiung 80424 Taiwan.

- H. H. C. Iu is with the School of Electrical and Electronic Engineering, The University of Western Australia, Crawley, WA 6009 Australia.

- S.-M. Kang is with the Jack Baskin School of Engineering, UC Santa Cruz, Santa Cruz, CA, 95064 USA.

Manuscript received July 1, 2020.

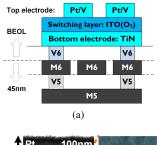

Fig. 1. (a) Schematic of a typical BEOL integration of a resistive random-access memory (RRAM) switching layer with a standard CMOS process (b) Transmission electron microscopy (TEM) image of the high-speed switching metal-insulator-metal memristor built for logic implementation.

which comes with 1) larger area consumption, 2) increased propagation delay, and 3) weaker noise tolerance due to an intermediate logic level. These partially offset the benefits of MLC.

Multi-level non-volatile memories, such as memristors, have generated renewed interest in building dense logic, both digital and multi-state [9], [10]. Two distinct categories of two-level logic have emerged using memristors: state-based logic, which stores the output as the resistance state, and conventional voltage-based logic. For example, material implication logic (IMPLY) and memristor-aided logic (MAGIC) use resistance to represent logic states [11], [12], but are burdened with substantial peripheral overhead [13]. Memristor ratioed logic (MRL) is likened to conventional CMOS logic, where the output voltage level defines the logical state [14].

Memristor-CMOS processes integrate nanoscale memristor devices with CMOS in the back end of the line (BEOL), which makes it possible to alleviate some of the above drawbacks. Firstly, area utilization is improved by embedding the memristor fabric upwards, rather than outwards [15]–[19]. This is depicted in Fig. 1. Other non-volatile memories, such as Flash, rely on floating gates which consumes silicon area.

Now that memristor-CMOS integration is available in commercial processes (e.g., TSMC 40 nm RRAM-process [20], STMicro 130 nm [21]), device variation is less of a barrier to industry use of memristor-CMOS technologies. Rather, the slow switching speed due to the wide band gap of oxide ions,

TABLE I TERNARY LOGIC GATES

| Logic Implementation | Logic Type   | Notation |

|----------------------|--------------|----------|

| Primitive Gates      | Ternary-AND  | TAND     |

|                      | Ternary-OR   | TOR      |

|                      | Ternary-NOT  | TI       |

| Combinational Gates  | Ternary-NAND | TNAND    |

|                      | Ternary-NOR  | TNOR     |

|                      | Ternary-XOR  | TXOR     |

|                      | Ternary-XNOR | TXNOR    |

| Data Handling Gates  | Ternary-MAX  | TMAX     |

|                      | Ternary-MIN  | TMIN     |

and limited endurance pose greater challenges. Fast switching speeds typically require subjecting memristors to very large electric fields, causing endurance degradation.

Ternary logic improves data density by computing at a higher radix than binary, but this is often done so at the expense of additional components and routing. This is mitigated by integrating memristors in the back end of the line, which enables substantially higher data density over conventional CMOS logic.

To reduce the burden of decreased noise margins in multilevel logic, our memristor shows a very high transconductance during switching (= 28.44 mV/dec), and has a built-in vanadium selector integrated as the top electrode. This enables threshold switching (≈0.4 V) without the addition of transistor selectors and reduces current leakage, which improves noise tolerance. This device has been integrated into an unbalanced ternary logic family summarized in Table I. Prior memristor-CMOS ternary logic designs use idealized memristor or transistor models [22]–[25]. There is a lack of physically feasible simulations and experimental demonstrations of a complete memristor-CMOS ternary logic family in the literature.

This paper systematically designs, simulates and experimentally verifies an integrated memristor-CMOS logic family using a standard 50 nm process. Our gates achieve state-of-the-art performance compared to other memristor-CMOS designs in terms of area, power and speed. We achieve data density improvements over conventional CMOS gates by a factor of 3.9–25.5 times, and speed improvements by a factor of 13 over state-of-the-art high-speed memristor ternary logic implementations. All SPICE netlists are documented and available online for reproduction of our results.<sup>1</sup>

In section 2, we will present the circuit of the primitive memristor-CMOS gates: TAND, TOR, and various forms of the TI gate. Section 3 will present ternary compound logic built using the primitive gates: TNAND, TNOR, TMAX, TMIN, TXOR, TXNOR. Specifically, TNAND and TNOR

TABLE II

TRUTH TABLE FOR POSITIVE TERNARY LOGIC GATES

| $\mathbf{v}_{\mathrm{in}1}$ | $\mathbf{v}_{\mathrm{in}2}$ | TAND | TOR | TNAND | TNOR | TXOR | TXNOR |

|-----------------------------|-----------------------------|------|-----|-------|------|------|-------|

| 0                           | 0                           | 0    | 0   | 2     | 2    | 0    | 2     |

| 0                           | 1                           | 0    | 1   | 2     | 1    | 1    | 1     |

| 0                           | 2                           | 0    | 2   | 2     | 0    | 2    | 0     |

| 1                           | 0                           | 0    | 1   | 2     | 1    | 1    | 1     |

| 1                           | 1                           | 1    | 1   | 1     | 1    | 1    | 1     |

| 1                           | 2                           | 1    | 2   | 1     | 0    | 1    | 1     |

| 2                           | 0                           | 0    | 2   | 2     | 0    | 2    | 0     |

| 2                           | 1                           | 1    | 2   | 1     | 0    | 1    | 1     |

| 2                           | 2                           | 2    | 2   | 0     | 0    | 0    | 2     |

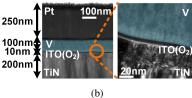

Fig. 2. MRL gates in [14] can be extended from binary logic to ternary logic. (a) TAND gate (b) TOR gate.

gates are constructed by cascading TAND and TOR gates with a TI gate. The TXOR and TXNOR gates are designed using Karnaugh map minimization. SPICE simulations are provided throughout, to validate each circuit as it is presented. Section 4 will provide details on device fabrication and characterization, and then demonstrate its performance as a ternary encoder and decoder. A study of area, power and switching speed are provided to compare against other memristor-CMOS ternary logic circuits.

# II. TERNARY LOGIC GATE DESIGN

Ternary logic can be divided into two types: balanced, which is expressed as (-1, 0, +1), and unbalanced. This latter unabalanced type comes in two forms, positive ternary (0, 1, 2) and negative ternary (-2, -1, 0) [26]. In this work, we focus on unbalanced positive ternary logic, where  $(0, 1, 2) = (GND, V_{DD}/2, V_{DD})$ . The truth table is given in Table II, where the output values of the TAND and TOR gates depend on the minimum and maximum values of the inputs, respectively.

# A. Ternary AND and Ternary OR

The TAND and TOR gates are a simple extension of MRL in [14], where two memristors are connected with alternating polarities, as shown in Fig. 2. However, in our ternary implementation, each input has three allowable states.

When the input voltages differ, the output voltage is determined by the voltage divider principle. As an example, consider the case  $v_{\rm in1} > v_{\rm in2}$  in the TAND gate from Fig. 2(a). Current flows from  $v_{\rm in1}$  to  $v_{\rm in2}$ , and the voltage across each device can be obtained from:

$$v_{\rm d1} = R_{\rm M1}i_1, \quad v_{\rm d2} = R_{\rm M2}i_2,$$

(1)

where  $v_{\rm d1}$  and  $v_{\rm d2}$  are the voltage drops across the two memristors,  $i_1$  and  $i_2$  are the currents flowing through the two

# TABLE III TAND AND TOR I/O CHARACTERISTICS

| Input                                 | TAND                                        | TOR                                         |

|---------------------------------------|---------------------------------------------|---------------------------------------------|

| $v_{\mathrm{in}1} = v_{\mathrm{in}2}$ | $v_{out} = v_{in1,in2}$                     | $v_{\rm out} = v_{\rm in1,in2}$             |

| $v_{\rm in1} > v_{\rm in2}$           | $v_{ m out} \approx v_{ m in2}$             | $v_{\mathrm{out}} \approx v_{\mathrm{in}1}$ |

| $v_{\rm in1} < v_{\rm in2}$           | $v_{\mathrm{out}} \approx v_{\mathrm{in}1}$ | $v_{\mathrm{out}} \approx v_{\mathrm{in}2}$ |

TABLE IV

MEMRISTOR MODEL PARAMATERIZATION

| Parameter                 | Description                      | Value        |

|---------------------------|----------------------------------|--------------|

| $R_{\rm ON}, R_{\rm OFF}$ | On/off resistance                | 100 Ω, 10k Ω |

| $V_{ON}, V_{OFF}$         | Set/reset voltage thresholds     | 0.2 V, 0.2 V |

| $\tau$                    | State variable time constant     | 500 ps       |

| T                         | Temperature                      | 298.5 K      |

| $x_0$                     | State variable initial condition | 0            |

branches within the gates, labeled in Fig. 2.  $R_{\rm M1}$  and  $R_{\rm M2}$  are the resistances of memristors  $M_1$  and  $M_2$ . The voltage divider principle gives us:

$$\frac{v_{\rm d1}}{v_{\rm d2}} = \frac{R_{\rm M1}}{R_{\rm M2}} = \frac{v_{\rm in1} - v_{\rm out}}{v_{\rm out} - v_{\rm in2}}.$$

(2)

This equation assumes there is negligible loading from fanout. As this may not necessarily be the case for memristive logic, we demonstrate a method to buffer stages using a source follower in our experimental results in Section IV. Assuming the voltage drops across each memristor are greater than the threshold for switching, a sufficient electric field is built up across each device causing them to switch. The bipolar switching characteristics of thin-film metal oxide memristors cause  $M_1$  to switch off  $(R_{M1} \rightarrow R_{OFF})$ , and  $M_2$  to switch on  $(R_{M2} \rightarrow R_{ON})$ . Assuming  $R_{OFF} >> R_{ON}$ , the output voltage  $v_{out}$  can be obtained as:

$$v_{\text{out}} = \frac{v_{\text{in}1}R_{\text{M2}} + v_{\text{in}2}R_{\text{M1}}}{R_{\text{M1}} + R_{\text{M2}}} = \frac{v_{\text{in}1}R_{\text{ON}} + v_{\text{in}2}R_{\text{OFF}}}{R_{\text{OFF}} + R_{\text{ON}}} \approx v_{\text{in}2}.$$

(3)

Note the output is approximate, as there is a small potential drop across  $M_2$ . This drop will increase with the fan-in of the gate, and imposes a limit on the allowable number of inputs for a TAND gate. It can be mitigated by using sufficiently high on/off resistance ratios (ideally a factor of 10 for two inputs). The same procedure above can be carried out for the TOR gate in Fig. 2(b) to give the following result:

$$v_{\text{out}} = \frac{v_{\text{in4}}R_{\text{M3}} + v_{\text{in3}}R_{\text{M4}}}{R_{\text{M4}} + R_{\text{M4}}} = \frac{v_{\text{in4}}R_{\text{ON}} + v_{\text{in3}}R_{\text{OFF}}}{R_{\text{ON}} + R_{\text{OFF}}} \approx v_{\text{in3}}.$$

(4)

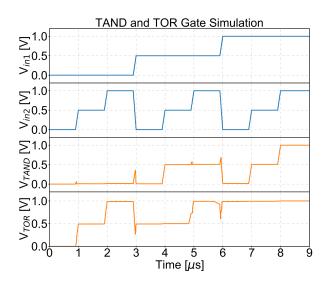

The output voltages are provided as a function of the input and summarized in Table III, which is consistent with Table II. The SPICE simulation results of all nine possible inputs to the TAND and TOR circuits are provided in Fig. 3, using Knowm's memristor model from [27]. The parameters used are provided in Table IV. The transistor models are from a 50 nm process (Level 54 BSIM4), and a supply of  $V_{\rm DD}$ =1 V. Detailed parameters can be found in the online repository containing the SPICE netlist [28].

3

Fig. 3. SPICE simulation results of the TAND and TOR gates for all input vectors. Transients in both output plots occur due to discontinuities in the memristor model.

Fig. 4. Proposed ternary inverter gate. (a) STI Schematic. (b) TI Truth Table.

# B. Ternary NOT

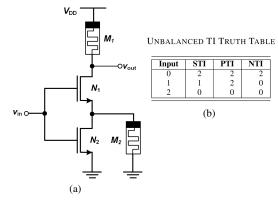

In unbalanced ternary logic systems, inverters can be classified into three categories: simple ternary inverters (STI), positive ternary inverters (PTI), and negative ternary inverters (NTI). As a supplement to Table II, the truth tables for the three inverters are given in Fig. 4(b).

1) STI Logic Gate: The STI gate is shown in Fig. 4(a). The NMOS transistor  $N_1$  must be 'stronger' than  $N_2$  (i.e., width  $W_1 > W_2$ , or bulk-to-source voltage  $V_{\rm BS1} > V_{\rm BS2}$ ), such that the threshold voltage  $V_{\rm TH1} < V_{\rm DD}/2$  and  $V_{\rm TH2} > V_{\rm DD}/2$ . The circuit operation in each of three modes is described below:

- Input Logic '0': when the input is grounded (logic '0'), both transistors are off, and the output is pulled up to V<sub>DD</sub> (logic '2') through M<sub>1</sub>. When connected to a load, M<sub>1</sub> will switch off as the negative electrode of the memristor is tied to V<sub>DD</sub>, ensuring a highly resistive current pathway for low static power dissipation.

- Input Logic '1': when the input is set to V<sub>DD</sub>/2, N<sub>1</sub> is turned on and N<sub>2</sub> remains off. Current will flow through the two memristors from V<sub>DD</sub> to ground. As a result, the

Fig. 5. Proposed PTI and NTI gates. (a) Schematic. (b) Circuit symbol.

resistance of both  $M_1$  and  $M_2$  will increase to  $R_{\rm OFF}$ . The resistive divider drives the output to  $V_{\rm DD}/2$ . Orienting the memristors with their negative electrodes positively biased ensures they will both switch off, thus minimizing current draw.

- Input Logic '2': when the input is set to V<sub>DD</sub>, both transistors are on. Consequently, the output terminal is shorted to ground through N<sub>1</sub> and N<sub>2</sub>.

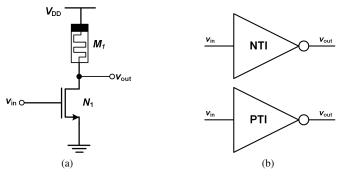

- 2) PTI and NTI Logic Gates: PTI and NTI gates have the same circuit structure, consisting of one memristor and one transistor. I.e., only the upper half of the STI gate is required (Fig. 5). However, the threshold voltage of  $N_1$  in the NTI must be below V<sub>DD</sub>/2, and above for the PTI which can be achieved by appropriate sizing (increasing W<sub>1</sub> for the NTI, decreasing W<sub>1</sub> for the PTI), or altering the substrate potential (increasing  $V_{\rm BS}$  for the NTI, decreasing  $V_{\rm BS}$  for the PTI). To illustrate, consider a DC sweep starting with  $V_{\rm in}=0$ . Initially,  $N_1$  is off, and so the output is pulled up trough  $M_1$ . An input logic 0 corresponds to an output logic 2. If the input is increased above the NTI threshold voltage (e.g., V<sub>DD</sub>/4 for optimal noise margins), then N<sub>1</sub> will pull the output down. Here, an input logic of 1 will correspond to an output of 0. However, as the PTI threshold (3V<sub>DD</sub>/4 for optimal noise margins) is higher than the NTI, the output will remain pulled up. Therefore, an input of logic 0 gives an output of logic 2.

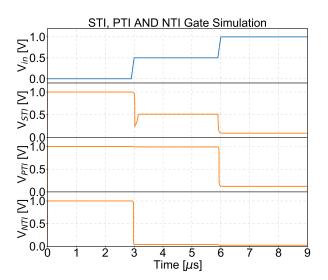

Driving the input all the way up to  $V_{\rm DD}$  will have no further effect on the NTI as  $N_1$  is already on. The PTI will behave similarly, as the  $N_1$  will also switch on. Therefore, an input of logic 2 will give a low output for both the PTI and NTI. Simulation results for the three classes of inverters are shown in Fig. 6 for all possible input cases, using the same memristor parameters previously given in Table IV. On inspection, the results are consistent with the truth table in Fig. 4(b).

#### III. COMBINATIONAL TERNARY LOGIC

The previous section presented and verified the TAND, TOR and TI gates via SPICE simulations. The following sections use these gates compositely to build the TNAND, TNOR, TMAX, TMIN, TXOR, and TXNOR gates.

# A. Ternary NAND and Ternary NOR

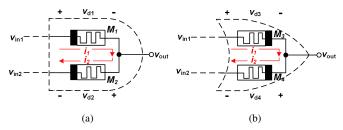

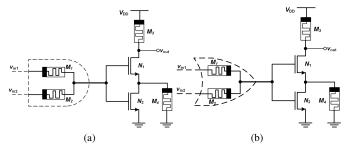

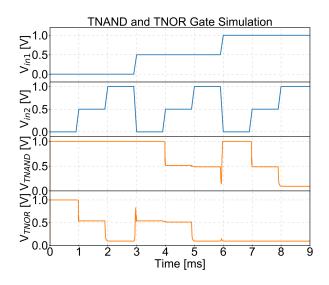

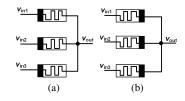

TNAND and TNOR gates can be intuitively constructed by connecting TAND and TOR gates to a STI gate, and is shown

Fig. 6. SPICE simulation results of the STI, PTI and NTI gates. Voltage transfer characteristics require a DC sweep, which neglects the time-dependence of memristors, and has therefore not been included in simulation results.

Fig. 7. Schematic of the proposed (a) TNAND gate, and (b) TNOR gate.

in Fig. 7. SPICE simulations are provided in Fig. 8. The finite output impedance of the TAND and TOR gates present no practical issues as the input to the next stage is effectively buffered by the large input impedance of the NMOS gates.

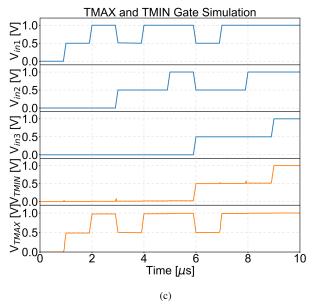

# B. Ternary Maximum and Minimum

As described in the previous section, TAND and TOR output the minimum and maximum value of the two inputs, respectively. This can be implemented by extending the inputs to the TAND and TOR gates shown in Fig. 9(a)-(b). SPICE simulations are shown in Fig. 9(c) using a 3-input gate, which verifies that the output of the TMIN gate is always the smallest of the input values, and the output of the TMAX gate is the largest of the inputs.

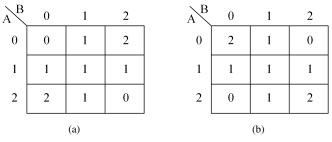

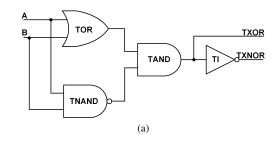

#### C. Ternary XOR and XNOR

In order to design the TXOR and TXNOR gates, we construct their Karnaugh maps (Fig. 10). Through minimization, we obtain the following logic functions:

$$A \, TXOR \, B = \overline{A}B + A\overline{B} = (A+B) \cdot (\overline{AB}) \tag{5}$$

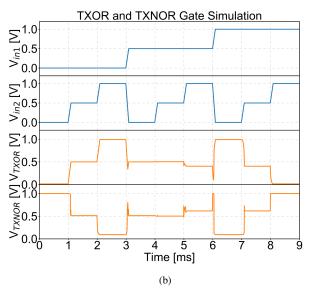

Fig. 8. SPICE simulation results of the TNAND and TNOR gates. Transients in both plots occur due to discontinuities in the memristor model, which also led to challenges for simulation convergence. The fix was to expand to a millisecond timescale. Note that this is a limitation of the numerical methods used in SPICE; our experimental results successfully realized nanosecond timescales, which will be shown in the following sections.

Fig. 9. Schematic of the (a) 3-input TMAX gate, and (b) 3-input TMIN gate. (c) SPICE simulation results.

$$A \ TXNOR \ B = AB + \overline{A} \overline{B} = \overline{(A+B) \cdot (\overline{AB})}$$

(6)

Fig. 10. K-map of the (a) TXOR gate, and (b) TXNOR gate.

Fig. 11. (a) Schematic of the TXOR and TXNOR gates based on the logic-level design presented in [29]. This is schematically the same as a standard binary XOR and XNOR gate. It is preferable here to use TOR and TAND gates as they occupy less chip area. (b) SPICE Simulation results. Logic stages with high output impedance must be buffered to be capable of driving subsequent stages, as was the case here. This is demonstrated in the experimental results.

A minimized gate level circuit can be constructed from (5) and (6), formed of a cascade of TAND, TOR, TNAND and TI gates, (Fig. 11(a)), with its corresponding SPICE simulation in Fig. 11(b).

### IV. EXPERIMENTAL RESULTS

In this section, we will briefly describe the process used to fabricate the ITO memristors, along with the parameters relevant to gate-level logic. This is important because this device enables us to overcome the difficulties in realizing a functional memristor-CMOS ternary logic family: namely, the fast switching speed, low voltage programming, and the

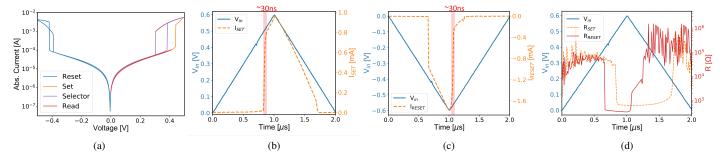

Fig. 12. Device characterization. (a) IV characteristic curve with set process occurring at approximately 0.4 V. (b) Set process switching time of approximately 30 ns. (c) Reset process. The first switch is a result of the selector turning on, before the memristor resets and absolute current suddenly drops. (d) RV characteristic curve showing an on/off ratio of over 15. The large variation in resistance is a result of sensing small nano- to microampere currents used in the calculation of resistance.

built-in selector which suppresses subthreshold currents. This device is then implemented as a ternary encoder and decoder to verify the correct operation of the gates presented in previous sections.

#### A. Device Fabrication

The memristor is a V/ITO(O<sub>2</sub>)/TiN MIM structure (Fig. 1(b)) fabricated in-house. We deposited a 200-nm-thick TiN layer as the bottom electrode using chemical vapor deposition on a Ti/SiO<sub>2</sub>/Si substrate. 10-nm of thin-film ITO is deposited via RF sputtering on an ITO target, Ar gas flow rate of 30 sccm and O flow rate of 20 sccm at 8 mtorr, which oxidizes the ITO film to create  $ITO(O_2)$ . The switching layer is patterned using a mask aligner process with a cell size of 600nm×600nm. The minimum transistor width used here is 500nm, which allows for reasonably good alignment between memristor and transistor. To form the top electrode, a 100-nmthick V layer is deposited via DC sputtering. Self-oxidation of the V layer creates a built-in selector. Therefore, this device integrates a one-selector-one-memristor (1S1R) cell into the same process, and is structurally simple to fabricate. Finally, Pt is deposited to prevent further oxidation of the top electrode. This completes the  $V/ITO(O_2)/TiN$  structure.

### B. Device Characterization

The device was characterized using a B1525A semiconductor parameter analyzer for pulse measurements, B1500 and B1505A for DC measurements, and B1530A for high-speed IV measurements. Fig. 12(a) shows the results of an I-V sweep using a peak amplitude of  $\pm 0.5$  V. The selector dominated operating region (colored red) ensures leakage suppression during subthreshold operation. Set and reset occur at approximately  $\pm 0.4$  V. Prior to setting the device, there is a narrow margin where the built-in selector switches on, enabling a read operation without setting the device. This is especially useful for storage class non-volatile memory, stateful logic, and neuromorphic computing. Note that this is a highly digital device which sets and resets rapidly with a very high transconductance. This can be seen in Figs. 12(b-d), where the subthreshold swing is measured to be 28.44 mV/dec, ensuring usable noise margins at low supply voltages. This

TABLE V  $V/ITO(O_2)/TIN$  DEVICE PARAMETERS

| Parameter Description |                            | Value                   |

|-----------------------|----------------------------|-------------------------|

| $R_{ON}, R_{OFF}$     | On/off resistance          | 100 Ω, $>$ 1.5k Ω       |

| $V_{ m SET}$          | Set voltage threshold      | 0.43 V±2.3%             |

| $V_{RESET}$           | Reset voltage threshold    | -0.43 V                 |

| $V_{ m SEL}$          | Selector voltage threshold | 0.37 V±4.1%             |

| $V_{FORM}$            | Forming voltage            | 1.3 V                   |

| $t_S$                 | Switching speed            | ≈30 ns                  |

| Device retention      |                            | >10 years @ 298 K       |

| Endurance             |                            | >10 <sup>5</sup> cycles |

fast switching action is expected to occur due to the use of a low-k switching layer, which highly concentrates the electric field. This also allows for a small forming voltage ( $\approx 1.3 \text{ V}$ ). A summary of memristor parameters is provided in Table V.

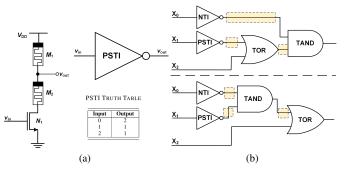

#### C. Ternary Encoder and Decoder

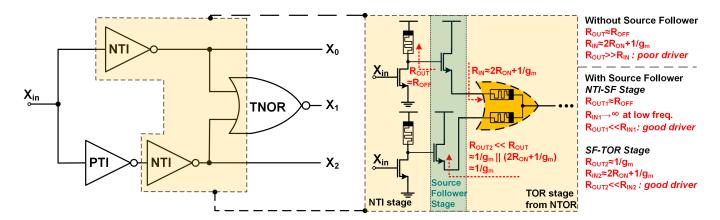

To experimentally verify the logic gates and device presented, we prototyped a ternary decoder and encoder at the board-level, using near-identical supply and threshold parameters to that of the NMOS transistors used in the simulations. We constructed a 1-to-3 decoder and a 3-to-1 encoder. The decoder takes a ternary input and generates three unary functions of either logic 0 or 2 at the output. Our design of the decoder consists of a PTI gate, two NTI gates, and a TNOR gate (Fig. 13). Note the finite output impedance of the NTI and PTI gates, which makes them poor drivers when cascaded to stages with low input impedance. Therefore, when connecting high output impedance stages (such as the NTI and PTI gates) to low input impedance stages (such as the TNOR gate), a source follower should be used as a buffer. Although this results in a small potential drop from the gate to source, it is boosted back up in subsequent stages. An alternative method is to use a minimum sized bleeder PMOS to restore charge to the output node. Another clear drawback is the necessity of an additional NMOS wherever a poor driver is connected to a low impedance gate. But as we have avoided the use of PMOS transistors by pulling up with memristors, and given that the memristor would be integrated in the BEOL, this consumes less chip area than a standard CMOS inverter, even with the additional logical state. An area analysis will be given in the

Fig. 13. Gate level schematic of the proposed ternary decoder, with transistor level depiction using a pair of source followers in between stages to improve the NTI as a driver. Here,  $g_m$  is the transconductance of the source follower,  $R_{\rm OUT}$  refers to the output resistance of the previous stage, and  $R_{\rm IN}$  is the input impedance to the following stage.  $R_{\rm OFF}$  and  $R_{\rm ON}$  are chosen here for the worst-case. Note that no additional source resistance is required for either source follower as the memristors from the TOR gate act as  $R_S$ . The above approximations of input and output impedance neglect channel-length modulation, but our experimental results demonstrate this is a reasonable assumption.

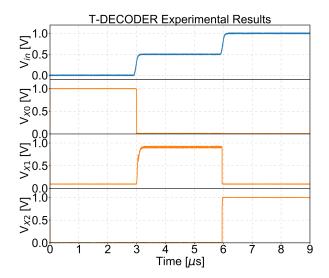

Fig. 14. Experimental results of the T-Decoder using a V/ITO( $\mathrm{O}_2$ )/TiN memristor.

Fig. 16. Experimental results of the T-Encoder using a  $V/ITO(O_2)/TiN$  memristor. The topology tested is the bottom circuit in Fig. 15(b).

next section. Experimental results of the ternary-decoder are provided in Fig. 14, which operates as expected on inspection.

Fig. 15. Schematic of the ternary encoder. (a) PSTI Gate, a variation of the STI gate which replaces the low logic level with the intermediate state. (b) Logic-level topologies of the ternary encoder.

A similar technique is adopted in the construction of a 3-to-1 encoder. This time, we introduce a PSTI inverter in Fig. 15(a) which behaves similarly to the STI inverter, but with the caveat that it does not fully pull down to 0. Rather, the output is limited by the resistive divider effect, and can only go as low as half the supply voltage. This is needed for the ternary encoder in Fig. 15(b), where an intermediate output must be generated from high and low input signals. Two alternative topologies are presented. The highlighted nodes must be buffered, which is achieved with a source follower in the same way as shown with the ternary decoder. Experimental results are shown in Fig. 16.

# V. COMPARISON AND DISCUSSION

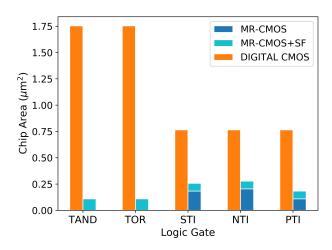

For a comparison against their digital CMOS counterparts, we designed the layout of the ternary logic gates using Cadence tools. An area and data density comparison is provided

|       | Si Area (μm²) | Si Area w/SF (μm²) | MR Area (μm²) | Proposed Size (%) | Data Density<br>Improvement | Data Density<br>Improvement w/SF |

|-------|---------------|--------------------|---------------|-------------------|-----------------------------|----------------------------------|

| TAND  | 0             | 0.10875            | 0.984         | 6.2               | $>10^{5}$                   | 25.5                             |

| TOR   | 0             | 0.10875            | 0.984         | 6.2               | >10 <sup>5</sup>            | 25.5                             |

| STI   | 0.1825        | 0.25625            | 0.984         | 33.5              | 6.6                         | 4.7                              |

| NTI   | 0.20375       | 0.2775             | 0.36          | 36.3              | 6.1                         | 4.4                              |

| PTI   | 0.10875       | 0.1825             | 0.36          | 23.9              | 11.1                        | 6.6                              |

| TNAND | 0.1825        | 0.25625            | 0.3650        | 25.9              | 8.5                         | 3.9                              |

| TNOR  | 0.1825        | 0.25625            | 0.3650        | 25.9              | 8.5                         | 3.9                              |

TABLE VI AREA AND DATA DENSITY COMPARISON USING A 50-NM PROCESS

Fig. 17. Silicon consumption of fundamental ternary logic gates compared to their digital CMOS equivalent in 50-nm process. Cases both with and without source-followers are considered.

#### TABLE VII POWER CONSUMPTION

|      | Static Power<br>Dissipation (µW) | Avg. Power (µW) |

|------|----------------------------------|-----------------|

| TAND | 98.54 [0 & 1]                    | 32.26           |

| TOR  | 95.73 [0 & 1]                    | 30.14           |

| STI  | 107.35 [1]                       | 54.16           |

| NTI  | 97.63 [1]                        | 65.76           |

| PTI  | 88.05 [1]                        | 40.79           |

in Table VI. The silicon area and memristor fabric consumed are treated separately as they are vertically integrated. The memristor used is described in the previous section, with a cell size of 600nm×600nm. The (proposed size)/(CMOS size) metric shows the silicon area consumption of our ternary gates in the worst-case (with an additional source follower stage included) as a proportion of the equivalent digital counterpart. This has also been depicted in the bar plot in Fig. 17. Data density improvement is calculated by multiplying the silicon area consumption improvement factor by the additional improvement gained in using ternary logic over digital logic. This improvement is quantified by a factor of log(3)/log(2)=1.58. In the case without the source-follower, the TAND and TOR gate area improvement would tend to infinity. To give a result that makes more sense, we have included the 65nm×65nm contacts required to connect the two memristors together in the top metal layer and treated that as silicon occupation. It is clearly evident that vertical integration of memristors gives an unparalleled advantage in data density over conventional CMOS logic.

The area of the NTI and PTI gates can be reduced by modifying body voltage, but we have again assumed worst-case in the absence of additional supply rails, and used transistor sizing to alter threshold. Another interesting result arises when comparing the area of STI and the NTI. Despite the NTI having a smaller transistor count, the STI is smaller due to sizing requirements. Most prior literature compares size on the basis of transistor count [23]–[25], [30], [31]. As is clear by this comparison, this practice does not give an accurate reflection of chip area utilized. When ternary logic is used, sizing is often determinative of operation and tends to outweigh the effect of transistor count.

Power consumption of the primitive gates are presented in Table VII. Static power dissipation is estimated at the worst-case using the listed inputs by taking the sum of the voltage-current product through each element. This is done using extraction from layout which passes DRC/LVS checks in Cadence. Average power dissipation is calculated by averaging the static power dissipation for every input combination. Ternary logic is typically designed by one of two methods: either using multiple supply rails, or by dividing down a single supply. In memristive logic, the latter strategy is utilized to avoid the need for charge pumps and additional power regulation. Therefore, memristive logic suffers from substantial power dissipation in comparison to its CMOS counterpart, which is on the order of tens of nanowatts.

A more fair comparison would be against other memristor-CMOS implementations of ternary logic, but there is a lack of any experimental results in the literature. The only complete memristor ternary logic experimental demonstration is at the device-level in Ref. [32]. Though power metrics are not reported, the forming voltage required for their device is in excess of 7 V, whereas our V/ITO(O<sub>2</sub>)/TiN device only requires 1.3 V. Their ZnO memristor requires milliamp compliance currents and relies on state-driven logic, which has been shown to have overhead CMOS circuitry over 50 times that of a conventional CMOS implementation [13]. Neglecting this overhead, we can make an estimation based on current draw alone that our power dissipation is an order of 10<sup>3</sup> times more efficient.

The work in [24] simulates a CNTFET TNOR gate which consumes 11.29 mW of power, and memristor-CNTFET TNOR gate which consumes 34.62 mW. For a fair comparison, we assume the memristors dominate power dissipation, and

normalize the on resistance value from 50  $\Omega$  to 100  $\Omega$ , so equivalent power dissipation would be approximately halved. Our TNOR implementation would then achieve close to an order of  $10^2$  better power efficiency.

A closer comparison point is available in [25], which simulates worst case static power in their TAND and TOR gates to be 8  $\mu$ W. We performed the analysis in our own design environment with modified parameters (on and off resistances are reduced by an order of magnitude from 1 K $\Omega$  to 100  $\Omega$ , 100 K $\Omega$  to 10 K $\Omega$ ; supply voltage is adjusted from 0.9 V to 1 V. An additional supply rail is also required in this work which we implemented using a resistive divider (a pair of 10 K $\Omega$  memristors), and determined our TAND gate consumes 61.6% of the total power, and our TOR gate consumes 59.8%, which is close to twice the improvement.

Speed is arguably the biggest shortfall of memristor-based logic when compared to conventional-CMOS logic. This occurs because of the large bandgap of ions which takes substantially more energy (and therefore time) to reprogram memristors over creating an inversion layer in a transistor channel. Conventionally, one would calculate the RC delay to estimate propagation delay of a logic gate, but the switching time of memristors will outweigh the RC delay in advanced processes. While the transit-time in the 50 nm process is 9.489 ps, there is simply no memristor logic family that can compete with this, unless implemented as resistor-transistor logic. Some prior literature reports picosecond propagation delays, but these are simulation results which idealize the gate delay as a function of only RC delay, and do not account for switching limits of memristors [23], [24]. Nonetheless, our fabricated memristor-CMOS ternary logic was comeptitive with other memristor-CMOS implementations. As noted in Table V, our memristor switching speed is approximately 30 ns. The switching speed in Ref. [32] is 400 ns, showing our work is an improvement by a factor of 13 over the only other device implementation of ternary memristor logic.

# VI. CONCLUSION

To our knowledge, this is the first hardware implementation of a complete memristor-CMOS ternary logic family. Therefore, we have provided sufficient area, power and speed metrics to enable future memristor-CMOS implementations to generate a figure-of-merit for future comparison. Our work demonstrates an implementation with extremely high data density. We have optimized for speed at the device level which outperforms all other ternary logic simulations using memristors, but it also highlights shortcomings in power and speed when compared to conventional CMOS. The highdensity gates we have designed can advance the state-of-theart in multi-level applications, such as storage class memory which demands high data density, and in ternary content addressable memories which perform a look-up operation to query between three different memory states. In the interest of reproducibility, all simulation data is available online by following the link provided in Ref. [28].

#### ACKNOWLEDGMENT

This work was supported by the National Natural Science Foundation of China under Grant No. 61871429, and the Natural Science Foundation of Zhejiang Province (Grant No. LY18F010012).

#### REFERENCES

- [1] C. C. Lu, et al.,, "Analysis and realization of TLC or even QLC operation with a high performance multi-times verify scheme in 3D NAND Flash memory", 2018 IEEE Intl. Electron Devices Meeting (IEDM), San Francisco, CA, USA, Dec 2018.

- [2] T. S. Jung, et al., "A 117-mm/sup 2/3.3-V only 128-Mb multilevel NAND flash memory for mass storage applications", *IEEE J. Solid-State Circuits*, vol. 31, no. 11, pp. 1575–1583, Nov. 1996.

- [3] A. Weber, "Multi-rate and multi-level gigabit interface converter", US Patent 7 174 106, Feb. 6, 2007.

- [4] J. Guerber, H. Venkatram, M. Gande, A. Waters and U. K. Moon, "A 10-b ternary SAR ADC with quantization time information utilization", *IEEE J. of Solid-State Circuits*", vol. 47, no. 11, pp. 2604–2613, Nov. 2012.

- [5] C. Y. Kung, C. P. Huang, C. C. Li and S. J. Chang, "A low energy consumption 10-bit 100kS/s SAR ADC with timing control adaptive window", 2018 IEEE Intl. Symp. on Circuits and Systems (ISCAS), Florence, Italy, May 2018.

- [6] C. Zhang, Y. Jing, Y. Huang and X. You, "Massive MIMO with ternary ADCs", *IEEE Signal Proc. Lett.*, vol. 27, pp. 271–275, Jan. 2020.

- [7] P. C. Balla and A. Antoniou, "Low power dissipation MOS ternary logic family", *IEEE J. Solid-State Circuits*, vol. 19, no. 5, pp. 739–749, Oct. 1984.

- [8] D. I. Porat, "Three-valued digital systems", Proc. of the Institution of Electrical Engineers, vol. 116, no. 6, IET, 1969.

- [9] J. K. Eshraghian, S. M. Kang, S. Baek, G. Orchard, H. H. C. Iu and W. Lei, "Analog weights in ReRAM DNN accelerators", 2019 IEEE Int. Conf. on Artificial Intelligence Circuits and Syst. (AICAS), Hsinchu, Taiwan, pp. 267–271, Mar. 2019.

- [10] J. Lee, J. K. Eshraghian, K. Cho and K. Eshraghian, "Adaptive precision CNN accelerator using radix-X parallel connected memristor crossbars", arXiv preprint arXiv:1906.09395, Jun. 2019.

- [11] S. Kvatinsky, D. Beolusov, S. Liman, G. Satat, N. Wald, E. G. Friedman, A. Kolodny and U. C. Weiser, "MAGIC – memristor-aided logic", eIEEE Trans. Circuits and Syst. II: Exp. Briefs, vol. 61, no. 11, pp. 895–899, Sep. 2014.

- [12] J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart and R. S. Williams, "'Memristive' switches enable 'stateful' logic operations via material implication", *Nature*, vol. 464, no. 7290, pp. 873-876, Apr. 2010.

- [13] X. Hu, M. J. Schultis, M. Kramer, A. Bagla, A. Shetty and J. S. Friedman, "Overhead requirements for stateful memristor logic", *IEEE Trans. Circuits and Syst. I: Reg. Papers*, vol. 66, no. 1, pp. 263–272, Jan. 2019.

- [14] S. Kvatinsky, N. Wald, G. Satat, E. G. Friedman, A. Kolodny and U. C. Weiser, "MRL – memristor ratioed logic", Proc. 13th Intl. Workshop on Cellular Nanoscale Network Appl., Turin, Italy, Aug. 2012.

- [15] J. K. Eshraghian, K. Cho, H. H. C. Iu, T. Fernando, N. Iannella, S. M. Kang and K. Eshraghian, "Maximization of crossbar array memory using fundamental memristor theory", *IEEE Trans. Circuits and Syst. II: Exp. Briefs*, vol. 64, no. 12, pp. 1402–1406, Oct. 2017.

- [16] Q. Xia, W. Robinett, M. W. Cumbie, N. Banerjee, T. J. Cardinali, J. J. Yang, W. Xu, X. Li, W. M. Tong, D. B. Strukov and G. S. Snider, "Memristor-CMOS hybrid integrated circuits for reconfigurable logic", *Nano letters*, vol. 9, no. 10, pp. 3640–3645, Sep. 2009.

- [17] M. R. Azghadi, et al., "Complementary Metal-Oxide Semiconductor and Memristive Hardware for Neuromorphic Computing", Advanced Intelligent Syst., vol. 2, no. 5, p. 1900189, Mar. 2020.

- [18] J. K. Eshraghian, et al., "Neuromorphic vision hybrid RRAM-CMOS architecture", IEEE Trans. Very Large Scale Integration (VLSI) Syst., vol. 26, no. 12, pp. 2816–2829, May 2018.

- [19] S. Baek, J. K. Eshraghian, S. H. Ahn, A. Jame and K. Cho, "A memristor-CMOS braun multiplier array for arithmetic pipelining", 2019 26th IEEE Intl. Conf. on Electronics, Circuits and Syst. (ICECS), pp. 735– 738, Nov. 2019.

- [20] Taiwan Semiconductor Manufacturing Corporation, 'eFlash', 2020. [Online] Available: https://www.tsmc.com/english/dedicatedFoundry/technology/eflash.htm. [Accessed: 23- May- 2020].

- [21] Circuits Multi-Projects (CMP), 'MAD200 Memory Advanced Demonstrator 200mm', 2018. [Online] Available: https://mycmp.fr/datasheet/mad200-memory-advanced-demonstrator-200mm. [Accessed: 23- May- 2020].

- [22] H. Zhang, et al., "Implementation of unbalanced ternary logic gates with combination of spintronic memristor and CMOS", Electronics, vol. 9, no. 4, p. 542, Apr. 2020.

- [23] N. Soliman, M. E. Fouda, A. G. Alhurbi, L. A. Said, A. H. Madian, A. G. Radwan, "Ternary functions design using memristive threshold logic", *IEEE Access*, vol. 16, no. 6, pp. 48371-48381, Apr. 2019.

- [24] N. Soliman, M. E. Fouda and A. G. Radwan, "Memristor-CNTFET based ternary logic gates", *Microelectronics J.*, vol. 72, pp. 74–85, Feb. 2018

- [25] M. Khalid and J. Singh, "Memristor based unbalanced ternary logic gates", *Analog Integrated Circuits and Signal Processing*, vol. 87, no. 3, pp. 399–406, Jun. 2016.

- [26] B. Mondal, P. Sarkar, P. K. Saha and S. Chakraborty, "Synthesis of balanced ternary reversible logic circuit", Proc. 43rd Intl. Symp. on Multiple Valued Logic, pp. 334-349, 2013.

- [27] W. T. Molter and M. A. Nugent, "The generalized metastable switch memristor model", CNNA 2016; 15th Intl. Workshop on Cellular Nanoscale Networks and their Applications, Dresden, Germany, Aug. 2016

- [28] J. K. Eshraghian, 'Code: Ternary Memristor-CMOS Logic', 2020. [Online] Available: https://www.jasoneshraghian.com/code. [Accessed: 25-May- 2020].

- [29] S. Lin, Y.-B. Kim and F. Lombardi, "CNTFET-Based design of ternary logic gates and arithmetic circuits", *IEEE Trans. on Nanotechnology*, vol. 10, no. 2, pp. 217–225, Mar. 2011.

- [30] P. V. Saidutt, V. Srinivas, P. S. Phaneendra and N. M. Muthukrishnan, "Design of encoder for ternary logic circuits", *IEEE 2012 Asia Pacific Conf. on Postgraduate Research in Microelectronics and Electronics*, pp. 85–88, Dec. 2012.

- [31] D. Etiemble, "Ternary circuits: why R=3 is not the optimal radix for computation", arXiv:1908.06841v1, Aug. 2019.

- [32] Y.-J. Zhang et al., "Implementation of all 27 possible univariate ternary logics with a single ZnO memristor", IEEE Trans. Electron Devices, vol. 66, no. 11, pp. 4710–4715, Sep. 2019.

Jason K. Eshraghian (S'16-M'19) is a Post-Doctoral Researcher at the Department of Electrical Engineering and Computer Science, University of Michigan in Ann Arbor. He received the Bachelor of Engineering (Electrical & Electronic) and the Bachelor of Laws degrees from The University of Western Australia, Perth, WA, Australia in 2016, where he also completed his Ph.D. Degree. From 2015 to 2016, he was a Research Assistant at Chungbuk National University, South Korea. Since 2019, he has an Analog Design Engineer Consultant with

HummTech developing non-invasive neurostimulator wearables. He is also a member of the IEEE Neural Systems and Applications Committee. His current research interests include neuromorphic computing and vision perception. Jason was awarded the 2019 IEEE Very Large Scale Integration Systems Best Paper Award, and the Best Paper Award at the 2019 IEEE Artificial Intelligence Circuits and Systems Conference.

Chih-Yang Lin is currently pursuing his Ph.D. degree at the Department of Physics, National Sun Yatsen University, where he also received his Bachelor's Degree in 2015. He has filed 17 patents including 5 U.S. patents, covering various electron devices. His research interests include non-volatile resistive-switching memory, selector devices, thin film transistors, and advanced MOSFETs.

Xiaoyuan Wang received the B.S. degree in Agricultural Electrification and Automation from Heilongjiang Bayi Agricultural University, Daqing, China in 2003, the M.S. degree in physical electronics from Harbin Institute of Technology, Shenzhen, China, in 2008, and the Ph.D. degree in electronical engineering from Harbin Institute of Technology, Harbin, China, in 2013. From 2010-2011, she was a Visiting Student with the University of Western Australia, Australia. In 2017, she was a visiting scholar with The University of Western Australia. Australia.

She is currently an Associate Professor with the School of Electronics and Information, Hangzhou Dianzi University. Her research interests include nonlinear dynamics, memristive systems, multiple-valued logic technologies, and signal processing. She has published over 40 papers in these areas.

Pengfei Zhou received his B.Eng. degree in Electronic and Communication Engineering from the School of Electronics and Information, Anhui Jianzhu University, China, in 2018. He is currently pursuing a M.S. degree in Electronic Science and Technology at Hangzhou Dianzi University. His current research interests are multi-valued memory elements mathematic modeling and memristor-based logic circuit design approaches.

Herbert Ho-Ching Iu (S'98–M'00–SM'06) received the B.Eng. (Hons) degree in electrical and electronic engineering from the University of Hong Kong, Hong Kong, in 1997. He received the Ph.D. degree from the Hong Kong Polytechnic University, Hong Kong, in 2000. In 2002, he joined the School of Electrical, Electronic and Computer Engineering, The University of Western Australia as a Lecturer. He is currently a Professor at the same school. His research interests include power electronics, renewable energy, nonlinear dynamics, current sensing

techniques, and memristive systems. He has published over 150 papers in these areas. He has won two IET Premium Awards in 2012 and 2014. In 2014, he also won the UWA Vice-Chancellor's Mid-Career Research Award. He received the 2019 IEEE Transactions on Very Large Scale Integration Systems Best Paper Award, and the Best Paper Award of 2019 IEEE International Conference on Artificial Intelligence Circuits and Systems. He currently serves as the Associate Editor-in-Chief for IEEE Journal on Selected and Emerging Topics in Circuits and Systems, Associate Editor for IEEE Transactions on Circuits and Systems II, IEEE Transactions on Power Electronics, IEEE Transactions on Network Science and Engineering, Editor for IEEE Transactions on Smart Grid, and International Journal of Circuit Theory and Applications. He is a Co-editor of Control of Chaos in Nonlinear Circuits and Systems (Singapore: World Scientific, 2009) and a co-author of Development of Memristor Based Circuits (Singapore: World Scientific, 2013).

Ting-Chang Chang Ting-Chang Chang received the Ph.D. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 1994. He is currently the Chair Professor with the Department of Physics, National Sun Yat-sen University, Kaohsiung, Taiwan. He has authored more than 500 articles in SCI journals. He holds 60 U.S. patents and 160 Taiwan patents. His current research includes thin film transistor, MOSFET, and resistive random access memory.

Sung-Mo "Steve" Kang Sung-Mo "Steve" Kang is a Distinguished Professor of Jack Baskin School of Engineering, UC Santa Cruz. He was the 15th president of Korea Advanced Institute of Science and Technology (KAIST); the 2nd Chancellor of the University of California, Merced; dean of engineering of the University of California, Santa Cruz; and department head of electrical and computer engineering at the University of Illinois at Urbana-Champaign. Kang is a fellow of IEEE, ACM, and AAAS. He holds 16 US patents, has authored ten

books, and published over 500 journal and conference papers. His current research interest includes memristors and memristive systems, neuromorphic computing, low-power VLSI design, and compact modeling for computer-aided design. He has obtained his Ph.D. from UC Berkeley, M.S. from State University of New York, Buffalo and B.S. (Summa Cum Laude) from Fairleigh Dickinson University, Teaneck, NJ.