# Double Synchronous Unified Virtual Oscillator Control for Asymmetrical Fault Ride-Through in Grid-Forming Voltage Source Converters

M A Awal <sup>1,1</sup>, Md Rifat Kaisar Rachi <sup>2</sup>, Hui Yu <sup>2</sup>, Iqbal Husain <sup>2</sup>, and Srdjan Lukic <sup>2</sup>

November 8, 2023

# Abstract

A double synchronous unified virtual oscillator controller (dsUVOC) is proposed for grid-forming voltage source converters to achieve synchronization to the fundamental frequency positive- and negative-sequence components of unbalanced or distorted grids. The proposed controller leverages a positive- and a negative-sequence virtual oscillator, a double-sequence current reference generator, and a double-sequence vector limiter. Under fault conditions, the controller enables to clamp the converter output current below the maximum value limited by the converter hardware while retaining synchronization without a phase-locked-loop (PLL) regardless of the balanced or unbalanced nature of grid faults. Consequently, balanced and unbalanced fault ride-through can be achieved without the need for switching to a back-up controller. The paper presents the systematic development of the double-synchronous structure along with detail design and implementation guidelines. Validation of the proposed controller is provided through extensive control-hardware-in-the-loop (CHIL) and laboratory hardware experiments.

<sup>&</sup>lt;sup>1</sup>North Carolina State University

<sup>&</sup>lt;sup>2</sup>Affiliation not available

# Double Synchronous Unified Virtual Oscillator Control for Asymmetrical Fault Ride-Through in Grid-Forming Voltage Source Converters

M A Awal, Member, IEEE, Md Rifat Kaisar Rachi, Student Member, Hui Yu, Student Member, Iqbal Husain, Fellow, IEEE, and Srdjan Lukic, Member, IEEE

Abstract—A double synchronous unified virtual oscillator controller (dsUVOC) is proposed for grid-forming voltage source converters to achieve synchronization to the fundamental frequency positive- and negative-sequence components of unbalanced or distorted grids. The proposed controller leverages a positive- and a negative-sequence virtual oscillator, a doublesequence current reference generator, and a double-sequence vector limiter. Under fault conditions, the controller enables to clamp the converter output current below the maximum value limited by the converter hardware while retaining synchronization without a phase-locked-loop (PLL) regardless of the balanced or unbalanced nature of grid faults. Consequently, balanced and unbalanced fault ride-through can be achieved without the need for switching to a back-up controller. The paper presents the systematic development of the double-synchronous structure along with detail design and implementation guidelines. Validation of the proposed controller is provided through extensive control-hardware-in-the-loop (CHIL) and laboratory hardware experiments.

Index Terms—Double synchronous unified virtual oscillator control (dsUVOC), unbalanced fault ride-through, grid-forming converter, unified virtual oscillator control (uVOC)

#### Nomenclature

| $L_1, L_2, C_f$        | LCL filter components.               |

|------------------------|--------------------------------------|

| $v_c$                  | Converter switch-terminal output.    |

| $v_r$                  | Controller output voltage.           |

| $i_1$                  | Converter-side current.              |

| $i_2$                  | Grid-side current.                   |

| $v_{poc}$              | Converter terminal voltage.          |

| $\hat{Z}_{g1}, Z_{g2}$ | Grid impedances.                     |

| $Z_F$                  | Fault impedances.                    |

| $P_0$                  | Real power set-point.                |

| $Q_0$                  | Reactive power set-point.            |

| $V_0$                  | Nominal voltage (L-N RMS) set-point. |

| $\omega_0$             | Nominal frequency set-point.         |

| v                      | Oscillator output voltage.           |

| i                      | Input current to oscillator.         |

| $\eta$                 | Synchronization gain.                |

| $\mu$                  | Magnitude correction gain.           |

| $R_0$                  | Active resistance.                   |

| $i_0$                  | Current reference.                   |

| $\underline{i}_0$      | Saturated current reference.         |

| N                      | Number of phases.                    |

This work has been supported by FREEDM Center research funds for the Green Energy Hub research project.

| $x_f$      | Fault flag.                       |

|------------|-----------------------------------|

| $x_r$      | Mode transition signal.           |

| $V_T$      | Under-voltage threshold.          |

| $I_m$      | Maximum current limit.            |

| $v_{TH}$   | Equivalent grid/network voltage.  |

| $Z_{TH}$   | Equivalent grid/network impedance |

| $\omega$   | Equivalent oscillator frequency.  |

| $\omega_g$ | Grid frequency.                   |

| $\delta$   | Power angle.                      |

| $Z_n$      | Virtual impedance.                |

Boldface notation is used to indicate space vectors in stationary  $\alpha\beta$  frame; complex vector and column vector notations such as  $\mathbf{i}=i_{\alpha}+ji_{\beta}=[i_{\alpha}\ i_{\beta}]^T\leftrightarrow[i_{a}\ i_{b}\ i_{c}]^T$ , are used interchangeably. Capital letters such as I are used for root-mean-square (RMS) values and  $\hat{(.)}$  denotes the peak value such as  $\hat{I}$ ;  $\underline{(.)}$  denotes saturated/ limited value by the controller. Positive- and negative-sequence components of a variable/quantity/ parameter are represented by the respective notations with + and - in the subscript.  $\|(.)\|$  denotes the Euclidean norm such as  $\|(\mathbf{i})\| = \sqrt{i_{\alpha}^2 + i_{\beta}^2}$ .

#### I. INTRODUCTION

Grid-forming (GFM) converters are believed to be the key enabling technology for high penetration of power electronics interfaced distributed energy resources into the power system [1], [2]. Furthermore, converter grid-forming capability is critical in forming resilient microgrids where the majority of generators may be inverter-interfaced. In both use cases, controlling and predicting the behaviour of the GFM converter during a fault is critical for resilient system operation.

As opposed to the *current-source* nature of conventional grid-following (GFL) converters, GFM converters are programmed to emulate a *voltage behind reactance* response. Consequently, despite their superior grid-supporting features such as voltage and frequency regulation and inertial support, GFM converters are prone to transient over-current under fault conditions. Due to their current-source type behavior, GFL converters provide excellent over-current limiting response, whereas without explicit fault management measures, GFM converters may experience excessive over-currents leading to hardware damage. Ride-through of symmetrical and asymmetrical faults remain one of the key challenges for GFM converters till date.

Early works on fault ride-through (FRT) by GFM converters rely on a separate set of back-up controllers which employ phase-locked-loop (PLL) based vector current controllers; a controller switch is performed as soon as a fault is detected [3]-[5]. To eliminate such controller switch under fault conditions, another class of FRT strategies have been proposed for GFM controllers consisting of cascaded voltage and current reference tracking loops beneath the real and reactive power control loops [6]. In this class of FRT controllers, explicit limits are imposed on the references to the inner current tracking loops to prevent excessive over-current under faults. However, this approach is prone to integral windup issues in the outer voltage and power control loops. In essence, under such scenarios the *power synchronization* action through transient transfer of active and reactive powers by the outer loops is cutoff due to windup and consequently synchronization is lost [7], [8]. A potential solution was presented in [8], where a proper coordination between the inner loops and the outer power control loops is used to prevent such windup phenomena. Another class of FRT controllers have also emerged which avoid such windup by means of dynamic virtual impedance [9], [10]. However, to fully utilize the converter's current capability, the required virtual impedance is dependent on the variable grid condition during fault, such as the depth of voltage sag and/or phase jump and grid impedance. An explicit current limiter provides a more intuitive and easier implementation [8].

Virtual oscillator based controllers, such as virtual oscillator control (VOC) and dispatchable virtual oscillator (dVOC), are another class of emerging GFM controllers which are designed for almost global synchronization guarantee in arbitrary N-converter networks with zero inertia [11]–[16]. These nonlinear time-domain controllers provide substantially faster synchronization compared to synchronous machine emulation based methods such as droop control and virtual synchronous machine (VSM) [17]. A unified virtual oscillator controller (uVOC) was recently proposed which inherits the rigorous theoretical foundation and asymptotic synchronization guarantee of dVOC and provides enhanced ride-through capability under symmetrical grid faults [18], [19]. Unlike conventional droop based methods, uVOC uses explicit current references in the power-synchronization loop, which offers a unique advantage for limiting over-current; current-limiters can be embedded directly in the synchronizing controller. Consequently, symmetrical FRT is achieved without the need for controller switch and/or dynamic virtual impedance. Furthermore, uVOC exhibits a first-order power-angle response [19], [20], i.e., fault-recovery is not constrained by any critical clearing angle (CCA) which constrains second-order controllers such as droop control and VSM.

Although, majority of reported literature focus on symmetrical FRT, asymmetrical faults, such as single-line-to-ground (SLG) and double-line-to-ground (DLG) faults, are more frequent in real systems. Asymmetrical FRT strategies for GFL converters have been developed from the primary motivation of protecting the converter hardware from excessive current stress and/or power oscillation [21]–[23]. In most GFL applications, these asymmetrical FRT strategies rely on a

decoupled double synchronous reference frame phase-lockedloop (DDSRF-PLL) for synchronization and vector current controllers in both sequences to limit the converter output current. A number of current reference generation schemes have been reported for different control objectives such as balanced current injection and constant real power flow. Asymmetrical FRT in GFM applications can be achieved by switching to a DDSRF-PLL based vector current controller under fault. However, synchronization issues of PLLs, specifically under weak grids, have been well-documented in literature [18], [24]. A number of PLL-free asymmetrical FRT approaches have been reported. In [9], instead of synchronizing to the unbalanced grid, pre-fault values of the frequency and voltage magnitudes are used under faults. In [25], [26], a set of two current controllers are used beneath the power control loops to limit the positive- and negative-sequence currents. In [10], the outer power control loops synchronize to the positive-sequence voltage while an adaptive virtual impedance combined with inner voltage and current control loops are used to limit output current under asymmetrical faults. Another class of asymmetrical FRT controllers have been proposed for GFM converters, which employ power-synchronization in both positive and negative sequences [27]-[29]. These early attempts focus on protection of the converter hardware through balanced power control and/or suppression of active power oscillation. However, detailed implementation guidelines and performance evaluation under realistic fault conditions have not been reported. Furthermore, no compatible asymmetrical FRT methods have been reported for oscillator based GFM controllers.

In this work, a double synchronous unified virtual oscillator controller (dsUVOC) is developed which employs two oscillators to achieve power synchronization to both positiveand negative-sequence fundamental frequency components of an unbalanced or distorted grid. Over-current limiting under fault conditions is achieved by integrating a double-sequence vector limiter on the sequence-current references used by the synchronizing oscillators. FRT under symmetrical or asymmetrical fault conditions with over-current limiting as well as voltage support and unbalance mitigation are achieved without the need for switching to a back-up controller or a PLL. The rest of the paper is organized as follows: first, the grid-tied VSC system of interest is presented. Second, the proposed dsUVOC structure is introduced. Third, the principle of operation through power synchronization in both sequences is explained. Fourth, control hardware-in-the-loop (CHIL) and laboratory hardware test results are presented to validate the proposed controller.

#### II. ASYMMETRICAL FRT IN GRID-TIED VSCS

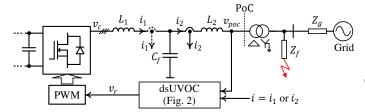

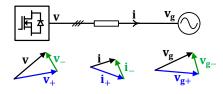

Fig. 1 shows a grid-tied VSC fed by a  $\Delta$ -Yg transformer. The converter operation under upstream asymmetrical faults, marked by the red arrow, is of interest. Note that the  $\Delta$  feeder connection prevents zero-sequence currents at the PoC, and hence only positive- and negative-sequence fault currents are of interest. Effective FRT is motivated by an underlying converter-oriented or system-oriented objective, constrained by

Figure 1. Grid-tied converter under study; red arrow denotes fault location at upstream of the  $\Delta$ -Yg feeder transformer.

the hardware capability, and must be enabled by an appropriate controller.

Under fault conditions, the overall control objective may vary in different applications and is set by a higher-level coordinator. For instance, converter-oriented FRT objective may be tailored to reduce stress on the converter hardware by minimizing active power oscillation, i.e., constant active power injection, or to equalize loading of all three phases, i.e., balanced current injection. System-oriented FRT objectives may be set to provide terminal voltage support at the PoC and/or unbalance mitigation. Naturally, converter-oriented FRT objectives are favored by manufacturers, whereas system operators may mandate system-oriented FRT objectives. However, relevant standards for desired FRT response by GFM converters are still under development and the lack of clear guidelines have led to different ride-through strategies. Standardization of such FRT objectives/responses requires extensive system-level research and consensus among various stakeholders such as converter manufacturers and system operators. Optimization of FRT objectives, such as optimum real and reactive power references for converter vs. system oriented objectives, are kept out of scope in this work. Instead, we focus on the FRT controller to enable simultaneous synchronization to positive- and negative-sequences of the grid, as well as to achieve flexible control capability for various converter-level and system-level objectives while respecting the hardware constraints.

Irrespective of the underlying objective, the hardware current capability/constraint must be respected during the FRT operation. Overall, for effective FRT, the controller must have two key capabilities; first, synchronization to the positiveand negative-sequence components of the asymmetric grid. Synchronization to only the positive-sequence component may suffice for specific converter-oriented objectives such as balanced current injection; however, more demanding objectives such as constant active power injection and voltage unbalance mitigation at PoC require synchronization to both positive- and negative-sequence grid voltage components. Second, fast overcurrent limiting is essential, specially when fault occurs and is cleared. Finally, proper coordination between the controller elements responsible for synchronization and for saturating output current is essential to retain synchronism under currentlimited operation. The following section describes the proposed dsUVOC structure followed by detailed explanations of how the various control capabilities are achieved.

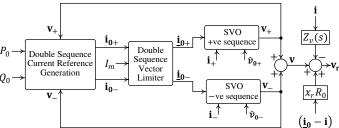

Figure 2. Proposed double synchronous unified virtual oscillator controller.

# III. DOUBLE SYNCHRONOUS UNIFIED VIRTUAL OSCILLATOR CONTROL

The dsUVOC implementation in a grid-tied VSC is shown in Fig. 1 where either the converter-side current  $i_1$  or the grid-side current  $i_2$  feedback can be used. No voltage or current reference tracking loops are used; the dsUVOC output is directly used by the pulse-width-modulator (PWM). The detail dsUVOC structure is shown in Fig. 2, which consists of a positive-sequence space vector oscillator (SVO), a negative-sequence SVO, a double-sequence current reference generator, and a double-sequence vector limiter. Furthermore, an active resistance  $R_0$  and virtual impedance  $Z_v(s)$  are used. The different components of the controller are described in the following subsections.

#### A. Positive- and Negative-Sequence Space Vector Oscillators

Historically, the bulk power system has relied on a very simple and natural synchronization process among large synchronous machines/generators. A traditional generator is designed to operate at the synchronous speed/frequency, such as 60Hz in the United States, when the nominal real power is drawn from its output terminals. While connected to an electrical grid, any increase (decrease) in a generator's operating speed with respect to the synchronous frequency of the grid leads to an increase (decrease) in its output power. Through governor action, an increase (decrease) in output power forces the generator to slow down (speed up). Thus, a generator achieves self-synchronization with the rest of the electrical grid through a transient exchange of power; this natural synchronization process through power-frequency drooping is termed as *Power Synchronization*. Power synchronization is leveraged as the fundamental synchronizing mechanism in synchronous machine emulation based GFM control approaches such as droop control, power synchronization control (PSC), and VSM. In [18], uVOC was shown to exhibit instantaneous power vs. frequency droop response which demonstrated the power synchronization nature of uVOC. In this work, the proposed dsUVOC leverages power synchronization in both positive- and negative-sequences to achieve synchronization to the fundamental-frequency sequence components of an unbalanced/distorted grid. The positive- and negative-sequence SVOs serve as the synchronizing units and are implemented

$$\dot{\mathbf{v}}_{+} = j\omega_{0}\mathbf{v}_{+} + j\eta_{+}(\underline{\mathbf{i}}_{0+} - \mathbf{i}_{+}) + \mu_{+}(\hat{V}_{0+}^{2} - \|\mathbf{v}_{+}\|^{2})\mathbf{v}_{+},$$

(1)

$$\dot{\mathbf{v}}_{-} = -j\omega_0 \mathbf{v}_{-} - j\eta_{-}(\underline{\mathbf{i}}_{0-} - \mathbf{i}_{-}) + \mu_{-}(\hat{V}_{0-}^2 - \|\mathbf{v}_{-}\|^2)\mathbf{v}_{-}.$$

(2)

The saturated current references  $\underline{\mathbf{i}}_{0+}$  and  $\underline{\mathbf{i}}_{0-}$  are generated from the SVO outputs  $\mathbf{v}_+$  and  $\mathbf{v}_-$  following the guidelines presented in Sections III-B and III-C. The sequence current components  $\mathbf{i}_+=i_{\alpha+}+ji_{\beta+}$  and  $\mathbf{i}_-=i_{\alpha-}+ji_{\beta-}$  of the converter output current  $\mathbf{i}=i_{\alpha}+ji_{\beta}$  are extracted as

$$\mathbf{i}_{\alpha+} = 0.5(i_{\alpha} - i_{\beta\perp}); \quad \mathbf{i}_{\beta+} = 0.5(i_{\beta} + i_{\alpha\perp}),

\mathbf{i}_{\alpha-} = 0.5(i_{\alpha} + i_{\beta\perp}); \quad \mathbf{i}_{\beta-} = 0.5(i_{\beta} - i_{\alpha\perp}).$$

(3)

Here,  $(.)_{\perp}$  denotes the orthogonal version of the respective signal obtained by delaying the original signal by  $T_0/4$ , where  $T_0$  is the fundamental period. The synchronization and magnitude correction gains are set as

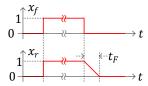

$$\eta_{+} = \eta_{-} = (1 + x_r/\tau_f)\eta_0; \ \mu_{+} = \mu_{-} = (1 - x_r)\mu_0.$$

(4)

The nominal values  $\eta_0$  and  $\mu_0$  are chosen following the design guidelines presented in [18], whereas the mode transition signal  $x_r$  is generated by appending a ramp-down to the trailing edge of fault signal  $x_f$  as shown in Fig. 3. The ramp-down over a short period  $t_F$  ensures smooth transition at fault clearing.

Figure 3. The mode transition signal  $x_r$  is generated from the fault signal  $x_f$ .

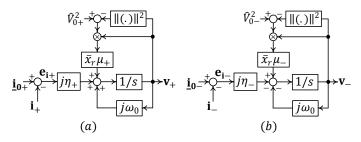

The implementations of the positive- and negative-sequence SVOs are shown in Fig. 4.

Figure 4. Implementation of synchronizing units - (a) positive-sequence SVO, (b) negative-sequence SVO.

The principle of operation of the two SVOs through power synchronization is presented in Section IV.

#### B. Double-Sequence Current Reference Generation

For a given set of real and reactive power references, the current references are generated using the controller internal states  $\mathbf{v}_+$  and  $\mathbf{v}_-$ . In [18], current references are generated using instantaneous power theory. However, for asymmetric operation the coupling between the power flows in the two sequences substantially complicates the current reference generation. Various current reference generation methods have

been proposed for asymmetrical FRT in GFL converters [21]–[23], [30]. For flexibility in control capability such as balanced current injection, constant real power flow, and positive and negative sequence reactive power compensation, the reference generation method reported in [22], [23] is adopted in this work. The sequence current references  $\mathbf{i_{0+}} = i_{\alpha 0+} + ji_{\beta 0+}$  and  $\mathbf{i_{0-}} = i_{\alpha 0-} + ji_{\beta 0-}$  are generated as

$$\mathbf{i}_{\alpha \mathbf{0}+} = \frac{2}{3} \left\{ \frac{k_{p+} v_{\alpha+}}{D_p} P_0 + \frac{k_{q+} v_{\beta+}}{D_q} Q_0 \right\},

\mathbf{i}_{\beta \mathbf{0}+} = \frac{2}{3} \left\{ \frac{k_{p+} v_{\beta+}}{D_p} P_0 - \frac{k_{q+} v_{\alpha+}}{D_q} Q_0 \right\},

\mathbf{i}_{\alpha \mathbf{0}-} = \frac{2}{3} \left\{ \frac{k_{p-} v_{\alpha-}}{D_p} P_0 + \frac{k_{q-} v_{\beta-}}{D_q} Q_0 \right\},

\mathbf{i}_{\beta \mathbf{0}-} = \frac{2}{3} \left\{ \frac{k_{p-} v_{\beta-}}{D_p} P_0 - \frac{k_{q-} v_{\alpha-}}{D_q} Q_0 \right\},$$

(5)

where  $D_p = k_{p+} \|\mathbf{v}_+\|^2 + k_{p-} \|\mathbf{v}_-\|^2$  and  $D_q = k_{q+} \|\mathbf{v}_+\|^2 + k_{q-} \|\mathbf{v}_-\|^2$ . Desired control objective can be obtained with proper selection of  $k_{p+}, k_{p-}, k_{q+}$ , and  $k_{q-}$  [23].

# C. Double Sequence Vector Limiter

To prevent over-current at the converter output under fault conditions, the current reference vector must be limited below the maximum value allowable by the converter hardware. A circular limiter used in [18], [19] cannot be used on asymmetric set of current references.

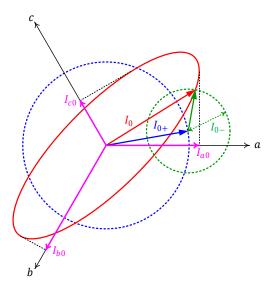

Figure 5. Asymmetric current vector follows an elliptical trajectory.

Fig. 5 illustrates the positive-sequence component  $I_{0+}$  and negative-sequence component  $I_{0-}$  of an arbitrary set of asymmetric current reference vector  $I_0$ . The instantaneous sum of the two inversely rotating vectors  $I_{0+}$  and  $I_{0-}$ , results in an elliptical trajectory of the total current vector  $I_0$ . For overcurrent limiting below the maximum RMS value  $I_m$  allowable by the converter hardware, the current reference is to be saturated as

$$\underline{\mathbf{i}}_0 = \{ [\underline{i}_{a0} \ \underline{i}_{b0} \ \underline{i}_{c0}]^T : \max\{\underline{I}_{a0}, \underline{I}_{b0}, \underline{I}_{c0}\} \le I_m \}, \quad (6)$$

First, the RMS magnitudes of the three-phase unsaturated current references are obtained as

$$I_{x0} = \left[ \{ \|\mathbf{i_{0+}}\|^2 + \|\mathbf{i_{0-}}\|^2 + 2(\xi_1 \cos 2\gamma - \xi_2 \sin 2\gamma) \} / 2 \right]^{1/2},$$

(7)

where  $\xi_1=(i_{\alpha0+}i_{\alpha0-}-i_{\beta0+}i_{\beta0-})$  and  $\xi_2=(i_{\beta0+}i_{\alpha0-}+i_{\alpha0+}i_{\beta0-})$  and  $\gamma=\{0,-2\pi/3,2\pi/3\}$  for phase x=a, b, and c, respectively. Next, the saturated current references are obtained as

$$[\underline{\mathbf{i}}_{0+} \ \underline{\mathbf{i}}_{0-}]^T = k_{sat}[\mathbf{i}_{0+} \ \mathbf{i}_{0-}]^T; \ k_{sat} = I_m/I_{max},$$

(8)

where  $I_{max} = \max\{I_{a0}, I_{b0}, I_{c0}\}$ . The active resistance  $R_0$  (see Fig. 2) is used for fast over-current limiting under fault condition. The various parts of the virtual impedance  $Z_v(s)$  are implemented as

$$Z_v(s) = \frac{R_v}{s/\omega_b + 1} + x_r \frac{L_v}{s/\omega_b + 1} + \sum_b Z_h(s),$$

(9)

where virtual resistance  $R_v$  can be used for augmenting system damping and the virtual inductance  $L_v$  can be used for fast over-current limiting at the fault instant [18], [19]; resonant filters  $\sum_h Z_h(s)$  can be added for harmonic current suppression [16]. Note that the complete controller shown in Fig. 2 is used under both nominal and fault conditions. As explained in Section IV-B, under normal operating condition with a symmetric grid voltage or under symmetric faults, the controller inherently achieves  $\mathbf{i}_{0-} = 0$  and  $\mathbf{i}_{-} = 0$ .

The level of voltage unbalance at the PoC is characterized by the unbalance factor (UF), defined as UF= $\|\mathbf{v_g}_-\|/\|\mathbf{v_g}_+\|$ . A fault signal is latched, i.e.,  $x_f=1$ , once an over-current is detected as  $|i_x|>\hat{I}_{Tf}, \forall x\in\{a,b,c\}$  in any of the phases or a voltage unbalance above a threshold  $K_{UTf}$  is detected as UF> $K_{UTf}$ . The fault is cleared, i.e.,  $x_f=0$ , once the positive-sequence voltage returns to the nominal range as  $\|v_+\|>\hat{V}_{Tc}$  and the UF falls below the clearing threshold  $< K_{UTc}$ .

#### IV. PRINCIPLE OF SYNCHRONIZATION

The proposed dsUVOC utilizes power synchronization in both positive- and negative-sequences. We consider the simplified system with an arbitrary operating point, shown in Fig. 6, where the virtual impedance and the LCL filter are lumped together with the source/grid impedance.

Figure 6. Simplified system for analysis of the double-sequence power synchronization.

# A. Positive-Sequence Synchronization

To illustrate the positive-sequence synchronization mechanism, we consider  $k_{p+}=1,\ k_{p-}=0,\ k_{q+}=1,\ k_{q-}=0;$  the negative-sequence SVO and the double-sequence vector

limiter on the current reference are excluded. Following similar steps used in [18], (1) can be rearranged as

$$\dot{\mathbf{v}}_{+} = [j(\omega_0 + \eta_+ e_{iP+}) + (\mu_+ e_{v+} - \eta_+ e_{iQ+})]\mathbf{v}_{+}, \quad (10)$$

where

$$e_{iP+} = \frac{2(P_{0+} - P_{+})}{3\|\mathbf{v}_{+}\|^{2}}; \quad e_{iQ+} = \frac{-2(Q_{0+} - Q_{+})}{3\|\mathbf{v}_{+}\|^{2}},$$

$$P_{+} + jQ_{+} = \mathbf{v}_{+}\mathbf{i}'_{+}; \quad P_{0+} + jQ_{0+} = \mathbf{v}_{+}\mathbf{i}'_{0+},$$

$$e_{v+} = \hat{V}_{0+}^{2} - \|\mathbf{v}_{+}\|^{2},$$

(11)

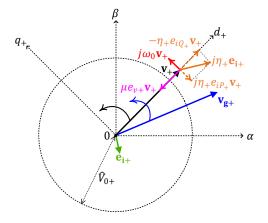

Figure 7. Power synchronization of the positive-sequence SVO.

and (.)' denotes complex-conjugate of the respective complex vector. Now, we consider a synchronous reference frame aligned with the positive-sequence SVO output voltage vector  $\mathbf{v}_+$ . For an arbitrary positive-sequence source/grid voltage vector  $\mathbf{v}_{\mathbf{g}}+$  and a current error  $\mathbf{e}_{\mathbf{i}+}=\mathbf{i}_{0+}-\mathbf{i}_{+}$ , a graphical representation of the SVO dynamics given by (10) is shown in Fig. 7, where the  $\alpha$  and  $\beta$  axes mark the stationary reference frame. Note that the real and imaginary parts of the complex coefficient of  $\mathbf{v}_+$  in (10) denote the instantaneous frequency  $\omega_+$  and normalized rate of change of the instantaneous vector magnitude  $(1/V_+)d(V_+)/dt$ , respectively [18], where  $V_+ = \|\mathbf{v}_+\|/\sqrt(2)$ . Evidently, instantaneous droop responses such as  $P_+$  vs.  $\omega_+$  and  $Q_+$  vs.  $V_+^2$  are observed on the SVO output voltage vector along the synchronous  $d_+$  and  $q_+$  axes, respectively as

$$\omega_{+} = \dot{\delta}_{+} = \omega_{0} + \frac{\eta_{+}}{3V_{+}^{2}} (P_{0+} - P_{+}),

\dot{V}_{+} = 2\mu_{+} V_{+} (V_{0+}^{2} - V_{+}^{2}) + \frac{\eta_{+}}{3V_{+}} (Q_{0+} - Q_{+}),$$

(12)

which facilitate the power synchronization to the positivesequence grid voltage vector  $\mathbf{v}_{\mathbf{g}+}$ .

### B. Negative-Sequence Synchronization

Excluding the positive-sequence SVO and taking  $k_{p+}=0$ ,  $k_{p-}=1$ ,  $k_{q+}=0$ ,  $k_{q-}=1$  and following similar notations as those used in the preceding subsection IV-A, the negative-sequence SVO dynamics in (1) can be rearranged as

$$\dot{\mathbf{v}}_{-} = [-j(\omega_0 + \eta_{-}e_{iP-}) + (\mu_{-}e_{v-} - \eta_{-}e_{iQ-})]\mathbf{v}_{-}.$$

(13)

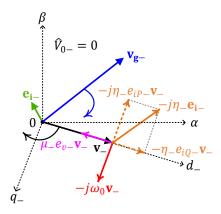

Figure 8. Power synchronization of the negative-sequence SVO.

For an arbitrary negative-sequence source/grid voltage vector  $\mathbf{v_{g-}}$  and a current error  $\mathbf{e_{i-}} = \mathbf{i_{0-}} - \mathbf{i_{-}}$ , a graphical representation of the SVO dynamics in the negative-sequence synchronous frame aligned with  $\mathbf{v_{-}}$  is shown in Fig. 8. Evidently, instantaneous droop responses such as  $P_{-}$  vs.  $\omega_{-}$  and  $Q_{-}$  vs.  $V_{-}^2$ , similar to those in the positive-sequence, are also obtained along the  $d_{-}$  and  $q_{-}$  axes, respectively as

$$\omega_{-} = \dot{\delta}_{-} = \omega_{0} + \frac{\eta_{-}}{3V_{-}^{2}} (P_{0-} - P_{-}),

\dot{V}_{-} = 2\mu_{-} V_{-} (V_{0-}^{2} - V_{-}^{2}) + \frac{\eta_{-}}{3V} (Q_{0-} - Q_{-}).$$

(14)

This enables power synchronization to the negative-sequence grid voltage vector  $\mathbf{v_{g-}}$ . Note that the negative-sequence voltage reference is set as  $\hat{V}_{0-}=0$  and under normal operation the power references are chosen as  $P_{0-}=0$  and  $Q_{0-}=0$  which leads to  $\mathbf{i_{0-}}=0$ ; for a balanced grid,  $\mathbf{v_{g-}}=0$  which results in  $\mathbf{v_{-}}=0$  and  $\mathbf{i_{-}}=0$ .

# C. Double-Sequence Synchronization

The current reference generation given by (5) uses total power references  $P_0$  and  $Q_0$  and results in sequence power references as

$$\frac{P_{0-}}{P_{0+}} = \frac{k_{p-} \|\mathbf{v}_{-}\|}{k_{p+} \|\mathbf{v}_{+}\|}; \quad \frac{Q_{0-}}{Q_{0+}} = \frac{k_{q-} \|\mathbf{v}_{-}\|}{k_{q+} \|\mathbf{v}_{+}\|}, \tag{15}$$

where  $k_{p-}=0$  and  $k_{q-}=0$  lead to  $P_{0-}=0$  and  $Q_{0-}=0$ , respectively. Symmetric and asymmetric faults can be distinguished by the voltage unbalance factor (UF). Under symmetric faults,  $k_{p-}=0$  and  $k_{q-}=0$  are used since negative-sequence compensation is not required. Now, using the full form of the current reference generation given by (5) and considering the double-sequence vector limiter, the positive- and negative-sequence droop responses during current constrained operation can be derived as

$$\omega_{+} = \omega_{0} + \frac{\eta_{+}}{3V_{+}^{2}} \left( \frac{2k_{p+}V_{+}^{2}}{D_{p}} k_{sat} P_{0} - P_{+} \right),

\dot{V}_{+} = 2\mu_{+}V_{+}(V_{0+}^{2} - V_{+}^{2}) + \frac{\eta_{+}}{3V_{+}} \left( \frac{2k_{q+}V_{+}^{2}}{D_{q}} k_{sat} Q_{0} - Q_{+} \right),

\omega_{-} = \omega_{0} + \frac{\eta_{-}}{3V_{-}^{2}} \left( \frac{2k_{p-}V_{-}^{2}}{D_{p}} k_{sat} P_{0} - P_{-} \right),

V_{-}^{2} = 2\mu_{-}V_{-}(V_{0-}^{2} - V_{-}^{2}) + \frac{\eta_{-}}{3V_{-}} \left( \frac{2k_{q-}V_{-}^{2}}{D_{q}} k_{sat} Q_{0} - Q_{-} \right).$$

(16)

Evidently, the  $P-\omega$  and the  $Q-V^2$  droop responses in both sequences are unaffected during current-constrained operation; only the power references are scaled proportionately with the voltage magnitude. Furthermore, the coupling among the two sequences exists through the power references. This enables the simultaneous double synchronous operation of the proposed controller.

#### V. EXPERIMENTAL RESULTS

#### A. Real-Time CHIL Test

A real-time controller hardware-in-the-loop (CHIL) test bed is set up to validate the proposed controller. The VSC system, shown in Fig. 1, including the feeder transformer and the grid are modeled in real-time OPAL-RT platform; grid-side current feedback is used for control implementation. The proposed dsUVOC is implemented using Texas Instruments' C2000 digital signal processor TMS320F28377s. The VSC ratings and the controller parameters are listed in Table I and Table II, respectively. The control parameters are selected following the design guidelines provided in [18]. Unbalance mitigation is prioritized for current reference generation using  $k_{p+} =$  $1, k_{p-} = 0, k_{q+} = 0.1$ , and  $k_{q-} = 0.9$ . The grid and fault impedances are set as  $Z_q = 0.019$  pu and  $Z_f = 0.019\%$  pu, respectively, with reactance to resistance ratio of X/R = 20. To evaluate the controller performance under different feeder strength at the PoC, we consider two different impedance values of the  $\Delta$ -Yg transformer as  $Z_{xer} = 0.1$  pu and 0.5pu. Note that the VSC ratings ( $V_0$  and  $P_{rated}$ ) are used as the base quantities for the pu notation. Therefore, the different values of  $Z_{xer}$  emulate different source strengths, i.e., shortcircuit ratio (SCR) while looking into the PoC from the VSC side.

Figure 9. CHIL FRT response to a SLG fault for  $Z_{xer}=0.5$ pu.

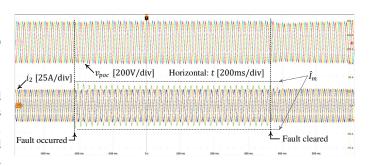

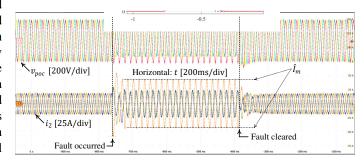

1) Single-Line-to-Ground (SLG) Fault: Fig. 9 shows the ride-through response to a SLG fault for a weak source/feeder

Table I Voltage Source Converter Ratings

| Symbol      | Parameter               | CHIL             | H/W Exp.           |

|-------------|-------------------------|------------------|--------------------|

| $S_{rated}$ | Rated power             | 10.8 kVA         | 3.3 kVA            |

| $P_{rated}$ | Rated real power        | 9 kW             | $2.75~\mathrm{kW}$ |

| $Q_{rated}$ | Rated reactive power    | 6 kVAR           | 1.8 kVAR           |

| $V_0$       | Nom. voltage            | 120 V            | 110 V              |

| $\omega_0$  | Nom. frequency          | $2\pi(60)$ rad/s | $2\pi(60)$ rad/s   |

| $f_{sw}$    | Switching frequency     | 10 kHz           | 50 kHz             |

| $f_s$       | Sampling frequency      | 20 kHz           | $25~\mathrm{kHz}$  |

| $L_1$       | Converter-side inductor | 0.046 pu         | 0.008 pu           |

| $L_2$       | Network-side inductor   | 0.058 pu         | 0.014 pu           |

| $C_f$       | Filter capacitor        | 0.036 pu         | 0.06 pu            |

Table II CONTROLLER PARAMETERS

| CHIL                |                      | H/W Exp. |                      |

|---------------------|----------------------|----------|----------------------|

| $\overline{\eta_0}$ | 16.63                | $\eta_0$ | 45.72                |

| $\mu_0$             | $7.1 \times 10^{-4}$ | $\mu_0$  | $8.4 \times 10^{-4}$ |

| $R_0$               | $0.52~\mathrm{pu}$   | $R_0$    | 0.38 pu              |

| $	au_f$             | 0.07                 | $	au_f$  | 0.07                 |

| $I_m$               | 1.2 pu               | $I_m$    | 1.2 pu               |

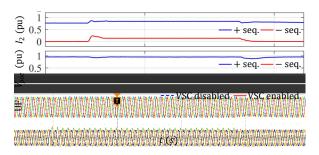

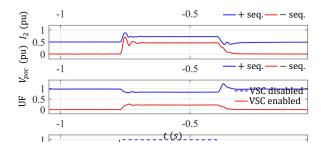

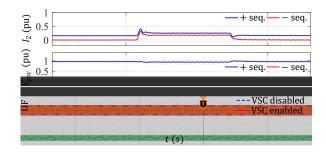

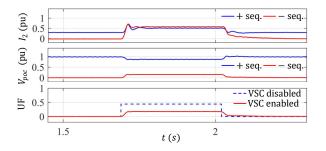

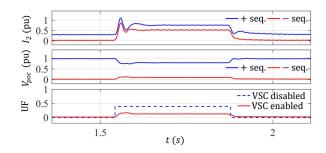

condition ( $Z_{xer}=0.5$  pu). At pre-fault condition the power references are set as  $P_0=0.75$  pu and  $Q_0=0$ . Once the fault is detected, the reactive power reference is set as  $Q_0=(S_{rated}^2-P_0^2)^{1/2}$ . The test data is further analyzed to evaluate the positive- and negative-sequence voltage and current magnitudes, and the UF at the PoC, which are shown in Fig. 10. Note that the converter output current is limited below the maximum allowable value  $\hat{I}_m$ . The positive-sequence voltage is boosted up as well as the UF, marked in red in Fig. 10, is improved/lowered compared to the uncompensated UF (marked by blue dashed line). The uncompensated UF is measured at the PoC separately under identical fault condition when the VSC is disabled. Once the fault is cleared, normal operation is quickly restored.

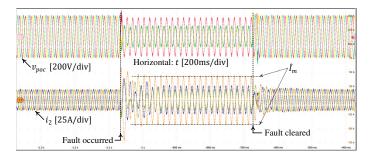

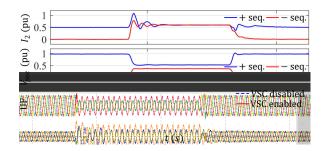

Next the experiment is repeated under a strong source/feeder condition with  $Z_{xer}=0.1$  pu and the corresponding results and data analysis are shown in Fig. 11 and Fig. 12, respectively. The output current is quickly limited below  $\hat{I}_m$  and the positive-sequence voltage at the PoC is restored under fault, whereas the negative-sequence voltage is lowered to improve

Figure 10. Analysis of test data for SLG fault for  $Z_{xer} = 0.5$ pu (Fig. 9).

Figure 11. CHIL FRT response to a SLG fault for  $Z_{xer} = 0.1$ pu.

Figure 12. Analysis of test data for SLG fault for  $Z_{xer}=0.1$  pu (Fig. 11).

the UF compared to the uncompensated UF under fault.

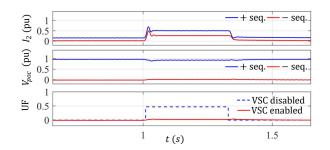

2) Double-Line-to-Ground (DLG) Fault: FRT response and the corresponding data analysis under a weak source/feeder condition ( $Z_{xer}=0.5~{\rm pu}$ ) are shown in Fig. 13 and Fig. 14, respectively.

Figure 13. CHIL FRT response to a DLG fault for  $Z_{xer}=0.5 \mathrm{pu}.$

Figure 14. Analysis of test data for DLG fault for  $Z_{xer} = 0.5$  pu (Fig. 13).

From the uncompensated UF, it is evident that the DLG fault leads to severe voltage unbalance at the PoC which results in momentary rise in the converter output current; however, the converter quickly limits the output current at the maximum allowable value  $\hat{I}_m$ . Leveraging the full current capability

(current saturated operation), the controller substantially improves the voltage UF at the PoC. Normal operation is restored quickly without any noticeable transients in the output current once the fault is cleared.

Figure 15. CHIL FRT response to a DLG fault for  $Z_{xer} = 0.1$ pu.

Figure 16. Analysis of test data for DLG fault for  $Z_{xer} = 0.1$  pu (Fig. 15).

Next the test is repeated under a strong source/feeder condition with  $Z_{xer}=0.1$  and the corresponding results are shown in Fig. 15 and Fig. 16, respectively. Due to the lower source impedance compared to that in the weak-source case (Fig. 14), a higher initial overshoot in converter output current is observed at the fault instant. The controller quickly limits the current at  $\hat{I}_m$  while lowering the PoC voltage UF. Note that the lower feeder impedance results in a lower improvement in the UF relative to Fig. 14 for the given current capability of the converter hardware.

# B. Laboratory Hardware Experiments

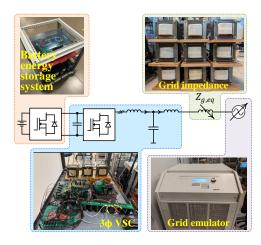

The laboratory test setup, including a battery energy storage system (BESS) and a three-phase VSC, is shown in Fig. 17; California Instruments' MX30pi programmable AC source is used as the grid emulator and discrete inductors  $Z_{g,eq}$  are used to obtain different grid strengths/SCRs. The BESS is rated at 400V 2.75kW and the VSC ratings are listed in Table I. The control parameters are shown in Table II. An observer based active damping (AD) controller is used to prevent LCL resonance in the VSC [31]. Texas Instruments' C2000 digital signal processor TMS320F28379D is used for digital control implementation.

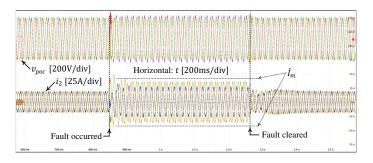

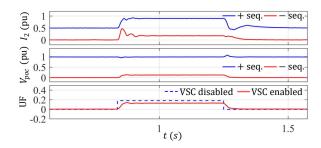

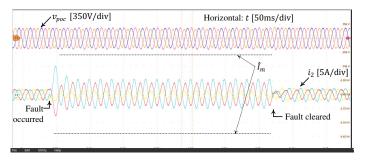

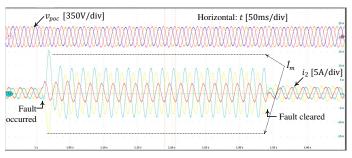

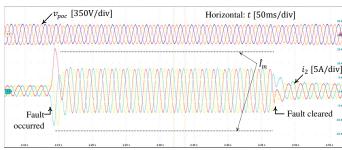

1) Single-Line-to-Ground Fault: A SLG fault is emulated by introducing a sudden voltage sag in one phase by the grid emulator (see Fig. 17). Fig. 18 and Fig.19 show the converter response to a SLG fault emulated by a sudden voltage sag on phase A from 1 pu to 0.27 pu for  $Z_{g,eq} = 0.57$ pu (SCR=1.75), while the reference is set as  $P_0 = 0.2$  pu. The experiment is

Figure 17. Test setup using a laboratory prototype.

repeated for  $Z_{g,eq}=0.19 \mathrm{pu}$  (SCR=5.25) and a voltage sag from 1 pu to 0.1pu; the corresponding FRT response and data analysis are shown in Fig. 20 and Fig. 21, respectively.

Figure 18. Experimental FRT response to a SLG fault for  $Z_{g,eq}=0.57$ pu (SCR = 1.75).

Figure 19. Analysis of test data for SLG fault for SCR = 1.75 (Fig. 18).

For both SCRs, the output currents are limited within the limit  $\hat{I}_m$  and the controller substantially improves the UF at the PoC. Normal operation is retained quickly once the fault is removed.

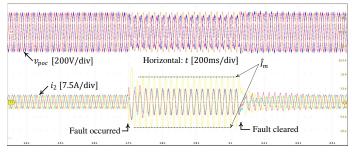

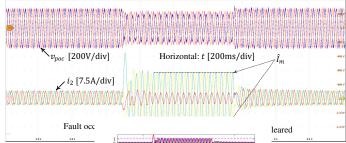

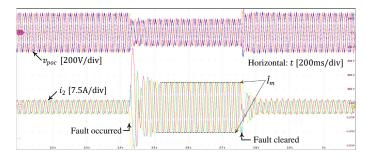

2) Double-Line-to-Ground Fault: A DLG fault is emulated by introducing a sudden voltage sag in two phases by the grid emulator (see Fig. 17). Fig. 22 and Fig.23 show the converter response to a DLG fault emulated by a sudden voltage sag on phase A and phase B from 1 pu to 0.27 pu for  $Z_{g,eq}=0.57$ pu (SCR = 1.75), while the reference is set as  $P_0=0.2$  pu. The experiment is repeated for  $Z_{g,eq}=0.19$ pu (SCR=5.25) and a voltage sag from 1 pu to 0.36 pu; the corresponding FRT

Figure 20. Experimental FRT response to a SLG fault for  $Z_{g,eq}=0.19 \mathrm{pu}$  (SCR = 5.25).

Figure 21. Analysis of test data for SLG fault for SCR = 5.25 (Fig. 20).

response and data analysis are shown in Fig. 24 and Fig. 25, respectively.

Figure 22. Experimental FRT response to a DLG fault for  $Z_{g,eq}=0.57 \mathrm{pu}$  (SCR = 1.75).

Figure 23. Analysis of test data for DLG fault for SCR = 1.75 (Fig. 22).

For both SCRs, the output currents are limited within the limit  $\hat{I}_m$  and the controller substantially improves the UF at the PoC. Normal operation is retained quickly once the fault is removed.

3) Three-Phase Fault: A three-phase fault is emulated by introducing a sudden voltage sag from 1 pu to 0.36 pu in all

Figure 24. Experimental FRT response to a DLG fault for  $Z_{g,eq}=0.19 \mathrm{pu}$  (SCR = 5.25).

Figure 25. Analysis of test data for DLG fault for SCR = 5.25 (Fig. 24).

three phases by the grid emulator.

Figure 26. Experimental FRT response to a three-phase fault for  $Z_{g,eq}=0.57 \mathrm{pu}$  (SCR = 1.75).

Figure 27. Experimental FRT response to a three-phase fault for  $Z_{g,eq}=0.19 \mathrm{pu}$  (SCR = 5.25).

Fig. 26 and Fig. 27 show the converter response to symmetrical three-phase faults for  $Z_{g,eq}=0.57 \mathrm{pu}$  (SCR=1.75) and  $Z_{g,eq}=0.19 \mathrm{pu}$  (SCR=5.25), respectively, with  $P_0=0.2 \mathrm{pu}$ . The controller leverages its allowable current capacity to improve the terminal voltage at the PoC in both cases. Consequently, the PoC voltage is raised to  $\approx 1 \mathrm{pu}$  and  $\approx 0.67 \mathrm{ms}$

pu for SCR=1.75 and SCR=5.25, respectively, while the output current is clamped below or at the allowable limit  $\hat{I}_m$ . Nominal operation is retained once the fault is cleared.

# VI. CONCLUSION

This work presents the first asymmetric FRT solution suitable for virtual oscillator based controllers. The proposed dsUVOC leverages simultaneous power synchronization in both positive- and negative-sequences, which enables synchronization to balanced, distorted, or unbalanced grids. Through sequence-decoupled as well as positive- and negative-sequence coupled space vector analysis, double-sequence power synchronization has been illustrated. This enhanced synchronization capability, combined with fast over-current limiting, facilitates ride-through of both symmetric and asymmetric faults. The proposed controller has been validated through real-time CHIL and laboratory hardware experiments.

#### REFERENCES

- [1] J. Matevosyan, B. Badrzadeh, T. Prevost, E. Quitmann, D. Ramasubramanian, H. Urdal, S. Achilles, J. MacDowell, S. H. Huang, V. Vital, J. O'Sullivan, and R. Quint, "Grid-Forming Inverters: Are They the Key for High Renewable Penetration?" *IEEE Power and Energy Magazine*, vol. 17, no. 6, pp. 89–98, Nov 2019.

- [2] R. Rosso, X. Wang, M. Liserre, X. Lu, and S. Engelken, "Grid-forming converters: an overview of control approaches and future trends," in 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 4292–4299.

- [3] K. O. Oureilidis and C. S. Demoulias, "A fault clearing method in converter-dominated microgrids with conventional protection means," *IEEE Transactions on Power Electronics*, vol. 31, no. 6, pp. 4628–4640, June 2016.

- [4] K. Shi, H. Ye, P. Xu, D. Zhao, and L. Jiao, "Low-voltage ride through control strategy of virtual synchronous generator based on the analysis of excitation state," *IET Generation, Transmission Distribution*, vol. 12, no. 9, pp. 2165–2172, 2018.

- [5] L. Zhang, L. Harnefors, and H. Nee, "Power-Synchronization Control of Grid-Connected Voltage-Source Converters," *IEEE Transactions on Power Systems*, vol. 25, no. 2, pp. 809–820, May 2010.

- [6] A. D. Paquette and D. M. Divan, "Virtual Impedance Current Limiting for Inverters in Microgrids With Synchronous Generators," *IEEE Transactions on Industry Applications*, vol. 51, no. 2, pp. 1630–1638, 2015.

- [7] L. Huang, L. Zhang, H. Xin, Z. Wang, and D. Gan, "Current Limiting Leads to Virtual Power Angle Synchronous Instability of Droop-Controlled Converters," in 2016 IEEE Power and Energy Society General Meeting (PESGM), 2016, pp. 1–5.

- [8] M. G. Taul, X. Wang, P. Davari, and F. Blaabjerg, "Current Limiting Control with Enhanced Dynamics of Grid-Forming Converters during Fault Conditions," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, pp. 1–1, 2019.

- [9] R. Rosso, S. Engelken, and M. Liserre, "Current Limitation Strategy For Grid-Forming Converters Under Symmetrical And Asymmetrical Grid Faults," in 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 3746–3753.

- [10] S. F. Zarei, H. Mokhtari, M. A. Ghasemi, and F. Blaabjerg, "Reinforcing Fault Ride Through Capability of Grid Forming Voltage Source Converters Using an Enhanced Voltage Control Scheme," *IEEE Transactions* on *Power Delivery*, vol. 34, no. 5, pp. 1827–1842, 2019.

- [11] B. B. Johnson, S. V. Dhople, A. O. Hamadeh, and P. T. Krein, "Synchronization of Parallel Single-Phase Inverters With Virtual Oscillator Control," *IEEE Transactions on Power Electronics*, vol. 29, no. 11, pp. 6124–6138, Nov. 2014.

- [12] M. Colombino, D. Groß, J. Brouillon, and F. Dörfler, "Global Phase and Magnitude Synchronization of Coupled Oscillators With Application to the Control of Grid-Forming Power Inverters," *IEEE Transactions on Automatic Control*, vol. 64, no. 11, pp. 4496–4511, February 2019.

- [13] G. Seo, M. Colombino, I. Subotic, B. Johnson, D. Groß, and F. Dörfler, "Dispatchable Virtual Oscillator Control for Decentralized Inverterdominated Power Systems: Analysis and Experiments," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), March 2019, pp. 561–566.

- [14] M. Lu, S. Dutta, V. Purba, S. Dhople, and B. Johnson, "A Grid-compatible Virtual Oscillator Controller: Analysis and Design," in 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 2643–2649.

- [15] J. Li, J. E. Fletcher, D. Holmes, and B. McGrath, "Developing a machine equivalent inertial response for a Virtual Oscillator Controlled Inverter in a machine-inverter based microgrid," in 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 4314–4321.

- [16] M. A. Awal, H. Yu, I. Husain, W. Yu, and S. M. Lukic, "Selective Harmonic Current Rejection for Virtual Oscillator Controlled Grid-Forming Voltage Source Converters," *IEEE Transactions on Power Electronics*, vol. 35, no. 8, pp. 8805–8818, August 2020.

- [17] Z. Shi, J. Li, H. I. Nurdin, and J. E. Fletcher, "Comparison of Virtual Oscillator and Droop Controlled Islanded Three-Phase Microgrids," *IEEE Transactions on Energy Conversion*, vol. 34, no. 4, pp. 1769– 1780, 2019.

- [18] M. A. Awal and I. Husain, "Unified virtual oscillator control for grid-forming and grid-following converters," *IEEE Journal of Emerg*ing and Selected Topics in Power Electronics, pp. 1–1, 2020, doi: 10.1109/JESTPE.2020.3025748.

- [19] M. A. Awal and I. Husain, "Transient stability assessment for current constrained and unconstrained fault ride-through in virtual oscillator controlled converters," *IEEE Journal of Emerging and Selected Topics* in *Power Electronics*, pp. 1–1, 2021.

- [20] H. Yu, M. A. Awal, H. Tu, I. Husain, and S. Lukic, "Comparative Transient Stability Assessment of Droop and Dispatchable Virtual Oscillator Controlled Grid-Connected Inverters," *IEEE Transactions on Power Electronics*, vol. 36, no. 2, pp. 2119–2130, February 2021.

- [21] A. Camacho, M. Castilla, J. Miret, J. C. Vasquez, and E. Alarcon-Gallo, "Flexible Voltage Support Control for Three-Phase Distributed Generation Inverters Under Grid Fault," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 4, pp. 1429–1441, 2013.

- [22] J. L. Sosa, M. Castilla, J. Miret, J. Matas, and Y. A. Al-Turki, "Control Strategy to Maximize the Power Capability of PV Three-Phase Inverters During Voltage Sags," *IEEE Transactions on Power Electronics*, vol. 31, no. 4, pp. 3314–3323, 2016.

- [23] J. Jia, G. Yang, and A. H. Nielsen, "A Review on Grid-Connected Converter Control for Short-Circuit Power Provision Under Grid Unbalanced Faults," *IEEE Transactions on Power Delivery*, vol. 33, no. 2, pp. 649–661, 2018.

- [24] D. Zhu, S. Zhou, X. Zou, and Y. Kang, "Improved Design of PLL Controller for LCL-Type Grid-Connected Converter in Weak Grid," *IEEE Transactions on Power Electronics*, vol. 35, no. 5, pp. 4715–4727, 2020.

- [25] B. Mahamedi, M. Eskandari, J. E. Fletcher, and J. Zhu, "Sequence-Based Control Strategy With Current Limiting for the Fault Ride-Through of Inverter-Interfaced Distributed Generators," *IEEE Transactions on Sustainable Energy*, vol. 11, no. 1, pp. 165–174, 2020.

- [26] T. Zheng, "Comprehensive control strategy of virtual synchronous generator under unbalanced voltage conditions," *IET Generation*, *Transmission Distribution*, vol. 12, pp. 1621–1630(9), April 2018. [Online]. Available: https://digital-library.theiet.org/content/journals/10. 1049/iet-gtd.2017.0523

- [27] P. Piya, M. Ebrahimi, M. Karimi-Ghartemani, and S. A. Khajehoddin, "Fault Ride-Through Capability of Voltage-Controlled Inverters," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 10, pp. 7933–7943, 2018

- [28] H. Just and S. Dieckerhoff, "Advanced negative sequence droop control for fault-ride-through operation and system support in weak grids," in 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, pp. P.1–P.10.

- [29] R. Vagner Ferreira, "Comparative Analysis of Techniques to Emulate Synchronous Machines in Grid-connected Converters," Ph.D. dissertation, Federal University of Minas Gerais, 2021.

- [30] M. Graungaard Taul, X. Wang, P. Davari, and F. Blaabjerg, "Current Reference Generation Based on Next-Generation Grid Code Requirements of Grid-Tied Converters During Asymmetrical Faults," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 4, pp. 3784–3797, 2020.

- [31] M. A. Awal, L. Della Flora, and I. Husain, "Observer Based Generalized Active Damping for Voltage Source Converters with LCL Filters," *IEEE Transactions on Power Electronics*, pp. 1–1, 2021.