# A Two-Stage 110VAC-to-1VDC Power Delivery Architecture Using Hybrid Converters for Data Centers and Telecommunication Systems

Ratul Das $^{1}$  and Hanh-Phuc Le $^{2}$

$^{1}$ University of California San Diego $^{2}$ Affiliation not available

November 1, 2023

## Abstract

Improving power delivery and management plays a key role in minimizing the cost of building and operating future green data centers to meet the fast growth of high-performance computing. Toward this important goal, this paper presents a new complete power delivery architecture to bridge AC grid voltages to core levels for computing loads using only 2 conversion stages with new converter topologies. The first stage converts a commercial AC line voltage of 90V-110V to a 48-60V intermediate bus with power factor correction (PFC). The second stage converts the bus voltage to core voltages of ~1 V with high current density and simple duty cycle control. Individually, the first stage was measured at 96.1% peak efficiency for output currents ranging in 0-4.5 A, while the second stage achieved 90.7% peak efficiency with a load range of 0-220 A at 1 V. Measured peak power densities are 73 W/in3 for the first stage and 2020 W/in3 for the second stage. In combination, the direct conversion from a line AC voltage of ~110 VAC to 1 VDC achieves a peak efficiency of 84.1% while providing output currents up to 160A.

# A Two-Stage 110VAC-to-1VDC Power Delivery Architecture Using Hybrid Converters for Data Centers and Telecommunication Systems

Ratul Das, Student Member, IEEE and Hanh-Phuc Le, Senior Member, IEEE

Abstract—Improving power delivery and management plays a key role in minimizing the cost of building and operating future green data centers to meet the fast growth of high-performance computing. Toward this important goal, this paper presents a new complete power delivery architecture to bridge AC grid voltages to core levels for computing loads using only 2 conversion stages with new converter topologies. The first stage converts a commercial AC line voltage of 90V-110V to a 48-60V intermediate bus with power factor correction (PFC). The second stage converts the bus voltage to core voltages of ~1 V with high current density and simple duty cycle control. Individually, the first stage was measured at 96.1% peak efficiency for output currents ranging in 0-4.5 A, while the second stage achieved 90.7% peak efficiency with a load range of 0-220 A at 1 V. Measured peak power densities are 73 W/in<sup>3</sup> for the first stage and 2020 W/in<sup>3</sup> for the second stage. In combination, the direct conversion from a line AC voltage of ~110 VAC to 1 VDC achieves a peak efficiency of 84.1% while providing output currents up to 160A.

#### I. INTRODUCTION

**M** any industrial and household devices today receive power from AC power distribution lines, while many of them are actually DC loads by nature. These DC loads have been increasing fast and their power requirements have become ever more stringent in recent years. Particularly, modern data centers and telecommunications systems also fall into this category where the final loads are high-performance processors that need a group of power converters to interface with AC distribution lines [1]. With the demand of modern data processing power, computation, and storage requirements, these processors have become excessively power-hungry that has ultimately translated into extremely high loading current, e.g., in many cases more than 1000 A, at low supply voltages of ~1 V.

Conventionally, high-performance computing rack servers in data centers are powered from an AC grid through four stages [2] : 1) A power factor correction (PFC) rectifier from the AC line voltage to high-voltage DC link bus, 2) the second stage converts the DC link to intermediate DC bus at 48 V nominally, 3) a 48V-to-12V high-efficiency DC-DC conversion, and 4) the last stage converts 12 V to core voltages of 0.8 V to 3.3 V. The series connection of multiple stages results in overall low power efficiency and density, leading to excessive heat which requires bulky and expensive cooling systems. As we are experiencing fast growth in data management and processing in recent days [3], [4], coupled with the introduction of 5G communications, artificial intelligence, crypto-currency, and cloud-dependent data processing and computations, this trend of power demand is only going to get more challenging. As a result, the traditional power delivery architecture becomes a critical bottleneck of the system performance and cost and thus, should be replaced with more advanced, optimized, and efficient ones.

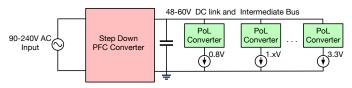

Reduced number of conversion stages with large conversion ratio converters can be one of the most viable approaches to adopt simplifying the power delivery rack and improving efficiency. With this motivation, in this work we demonstrate an efficient AC-to-core power delivery architecture for data centers and telecommunication systems comprised of only two direct conversion stages: 1) AC to 48-60V step-down PFC rectifier and 2) 48-60V to 0.8V-3.3V DC-DC converter stages. The proposed power delivery architecture is shown in Fig. 1.

The two converter stages have been designed employing hybrid converters that take advantage of both switched capacitor and inductor operations for better efficiency and power density. The PFC rectifier stage in this work utilizes a new multi-level hybrid converter based on partial series-parallel switched-capacitor operations to reduce inductor value and total harmonic distortion. It also steps down and moves the DC link to a lower voltage level, at 48-V nominal, where high-density capacitors can be utilized for energy buffer. Employing fast input current and slower output voltage control loops, this converter can simultaneously regulate the output voltage and input current to maintain good power factors and efficiency. The last-centimeter point of load (PoL) converter in this demonstration is a GaN-based multi-phase multi-inductor hybrid (MP-MIH) converter that was designed to provide very high output currents at low voltages with very high current density. This paper is organized as follows. Section II and III discuss the PFC step down and the MPMIH converter in detail with operations and design considerations respectively. Section IV presents the experimental results. We will summarize and conclude the paper in Section V.

Fig. 1: New Power Delivery Architecture

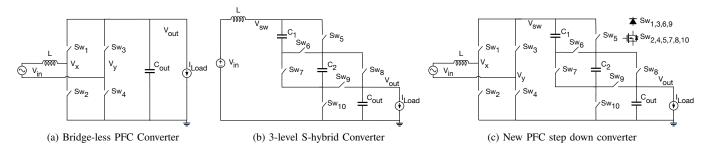

Fig. 2: S-hybrid Converter and derived PFC converter

# II. PFC STEP DOWN CONVERTER

Traditional AC-DC conversion with moderate to high power generally uses a bridge-less [5] or totem pole PFC converter shown in Fig. 2a. In these converters, Vout is maintained at a higher voltage than the peak voltage of the AC input voltage, V<sub>m</sub>. With suitable modulation scheme, the switching nodes,  $V_x$  and  $V_y$  are connected to either  $V_{out}$  or ground as required to maintain the average voltage of V<sub>xy</sub> over a switching period equal to Vin. This operation ensures a wellmaintained average input current proportional to the input voltage to obtain a high power factor. There are different control schemes adopted to regulate input current and output voltage to support the basic operation of this converter [6]. While this operation can achieve a very good displacement power factor or near zero phase lag between the input voltage and current, the distortion power factor can still deteriorate because of switching current ripple at high input voltages. Switching current ripple magnitude can be made smaller with larger input inductance, higher switching frequency, and/or lower voltage stress. While increasing the inductance requires a larger sized inductor that leads to lower power density, increasing switching frequency may not be desirable because an optimal value is highly dependent on particular semiconductor devices and core materials of the inductor. From this consideration, topological modifications that allow smaller voltage stress on the input inductor and active devices can be a better solution to achieve the design goal.

The modular multilevel converter has been popular for its topological advantages and widely used in DC-AC applications. There are also reports on switched-capacitor architectures for conversion from a single DC voltage to a high voltage AC output [7]-[9]. However, the converter type is found much less explored in AC-DC conversion applications. In this work, the architecture of an S-hybrid converter [10] has been modified and merged with a bridge-less or totem pole PFC converter for AC-DC applications. S-hybrid converter is a step-down hybrid DC-DC converter extended from a switched-capacitor (SC) converter with an inductor at the input, i.e. an inductor-first structure in step-down conversion. This architecture allows small input current stress on the inductor, leading to reduced conduction loss, in addition to the benefits of low voltage stress on active devices [10]. A 3-level s-hybrid converter in this category is shown in Fig. 2b. This converter comprises an inductor at its input and a partial series-parallel network for step-down operation that allows the

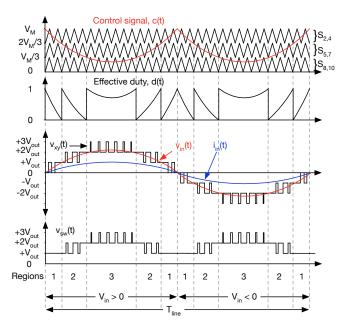

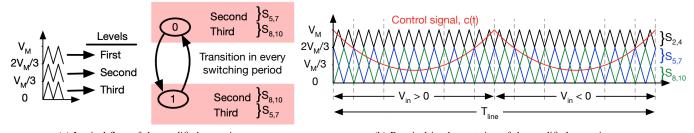

Fig. 3: Ideal operational waveforms

inductor to be switched in 3 small voltage domains of the input voltage. The combination of this converter with the bridge-less PFC converter in Fig. 2a results in the new final PFC step-down hybrid converter depicted in Fig. 2c.

#### A. Topology and Operation

As shown in Fig. 2c, the presented PFC step-down hybrid converter has one current shaping inductor, L, and four switches,  $Sw_{1-4}$  in the main rectifier. These switches operate at high frequency during the fraction of the line cycle at low voltage, while staying idle, on or off, for the remaining time. A switched-capacitor (SC) circuit follows the rectifier to provide the stepped down output as well as multilevel switching voltages for the inductor. In this demonstration, the SC circuit has two flying capacitors  $C_{1-2}$  and six switches  $Sw_{5-10}$ . These switches also operate at the converter's operating frequency during designated periods of the line cycle.

Figure 3 depicts the simplified ideal operational waveforms of the full converter during a full line cycle. All capacitors are expected to have negligible voltage ripples and equal voltages. Assume an input voltage with a peak value of  $V_m$  such that  $2V_{out} \le V_m < 3V_{out}$ , the full line-cycle can be divided into three time regions: 1) region 1:  $0 \le |V_{in}| < V_{out} \ge 2V_{out} \le |V_{in}| < 2V_{out}$ , and 3) region 3 :  $2V_{out} \le |V_{in}| < 3V_{out}$ . For

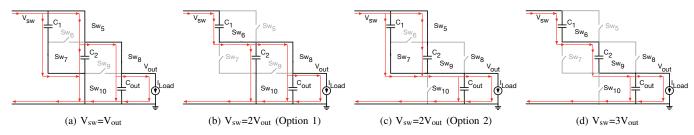

Fig. 4: SC configurations to generate different switching node voltages

any of these regions, the converter switches are operated in such a way that,  $V_{xy}$  switches in a pulse-width-modulated (PWM) control manner between the upper and lower limit of the region to generate an average voltage equal to  $V_{in}$ . The rectifier switches,  $Sw_{1-4}$ , take care of selecting the right polarity of  $V_{xy}$  in accordance with the input voltage being positive or negative. As a result,  $V_{xy}$  switches among 7 levels  $(0, \pm V_{out}, \pm 2V_{out} \text{ and } \pm 3V_{out})$ .

The SC configurations to generate different switching node  $V_{sw}$  voltages suitable for different input voltage levels are shown in Figure 4. In operation,  $Sw_{5,7}$  turn ON and OFF together while  $Sw_6$  is their complementary switch. In a similar way,  $Sw_9$  is the complimentary of  $Sw_{8,10}$ . The rectifier switches,  $Sw_{1-4}$  bridges the SC configurations with the input inductor and the source. In this proof of concept demonstration,  $Sw_{1,3,6,9}$  are implemented with diodes for simplicity while  $Sw_{1,2,5,7,8,10}$  are implemented with MOSFETs to control the operation of the converter. The switch selection for the main rectifier has been done following a standard bridge-less PFC converter design [5].

In order to control the switches, PWM control signals can be acquired by comparing a control signal c(t) with 3 separate carrier signals at 3 different voltage domains, as shown in Fig. 3. The control signal can be generated weighing regulation information of output voltage and input current in accordance with required output power and the input voltage. Particularly, when c(t) is in the first region, Sw<sub>2</sub> is switched at the carrier frequency when V<sub>in</sub>>0, while switching of Sw<sub>4</sub> is activated when V<sub>in</sub><0. Sw<sub>5,7</sub> and Sw<sub>8,10</sub> are activated with c(t) in the second and third regions, respectively. In a practical implementation with digital PWM modules in a micro-controller, effective duty cycle, d(t), can be calculated digitally based on similar information and used to generate the PWM signals. Following [10], d(t) can be calculated as:

$$d(t) = \begin{cases} 1 - \frac{|V_{in}|}{V_{out}} & \text{when, } 0 \le |V_{in}| < V_{out} \\ 2 - \frac{|V_{in}|}{V_{out}} & \text{when, } V_{out} \le |V_{in}| < 2V_{out} \\ 3 - \frac{|V_{in}|}{V_{out}} & \text{when, } 2V_{out} \le |V_{in}| < 3V_{out} \end{cases}$$

(1)

Utilizing Eqn. 1 and assuming  $V_M = 1$ , a separate set of expressions for d(t) can be derived in terms of c(t) which is useful to directly generate the PWM signals for the switches using different PWM modules in micro-controller:

$$d(t) = \begin{cases} 3c(t) - 2 & \text{when, } \frac{2}{3} \le c(t) \\ 3c(t) - 1 & \text{when, } \frac{1}{3} \le c(t) < \frac{2}{3} \\ 3c(t) & \text{when, } 0 \le c(t) < \frac{1}{3} \end{cases}$$

(2)

Note that, the switches in the SC circuit blocks 3x times smaller voltages compared to the switches in the main rectifier. Therefore, these switches can be selected with a smaller voltage rating, lower  $R_{DS,on}$ , and lower parasitic capacitance to improve overall performance with reduced conduction and switching losses.

#### B. Modified Operation for Capacitor Balancing

In the operation described with Fig. 4, flying capacitors C1-2 and output capacitor Cout are placed either parallel or stacked in series to generated  $V_{out}$ ,  $2V_{out}$  and  $3V_{out}$  levels at the switching node, V<sub>sw</sub>. To generate 2V<sub>out</sub>, C<sub>1</sub> can be stacked on top of  $C_2$  and  $C_{out}$  (configuration option 1) in Fig. 4b, or a parallel combination of  $C_1$  and  $C_2$  is placed on top of C<sub>out</sub> in Fig. 4c (configuration option 2). Although theoretically capable of supporting the 2Vout needed for operation, using only one of these configurations causes high capacitor voltage ripple problem for capacitor  $C_1$  and  $C_2$  in region 3, where,  $V_{sw}$  is switched between  $2V_{out}$  and  $3V_{out}$ . Particularly, if only configuration option 1 is used, C1 keeps receiving charges without redistribution to lower capacitors as the converter stays in region 3. On the other hand, if only configuration option 2 is used, both C1 and C2 keep receiving charge without redistribution to Cout and the load. The excessive charge for the flying capacitor(s) in region 3 where the input current is at its peak will cause a high voltage ripple, significant hard-charging loss, and risks of over-voltage damages for both capacitors and active switches. In addition, the overcharged voltage in the flying capacitors also causes unwanted

(a) Logical flow of the modified operation

(b) Practical implementation of the modified operation

Fig. 5: Modified operation

Fig. 6: Comparison of current ripples of the step down PFC converter (90Vrms-to-48V/4A) and bridge-less PFC converter (90Vrms-to- $3 \times 48V/4/3A$ ) for same output power operation with  $47 \,\mu\text{H}$  inductor and  $600 \,\text{kHz}$  switching frequency

variations in the average voltage of  $V_{xy}$  which in turn distorts the current waveform, increases current harmonics, and reduce power factor.

The overcharging problem in flying capacitors was identified in [7] for a demonstration of an inverter with slightly different topology and operation. It was also suggested to size the flying capacitor large enough to keep the over-voltage within a certain range. However, this method becomes less effective in high power applications where the input charging current is large, or very large capacitors are required. To avoid spending excessive area for more capacitance, in this work we introduce a relatively simple operational solution to solve this problem.

Recognizing that the key to the solution is charge redistribution among the flying capacitors and to the output capacitor, we combine and alternate both configurations, option 2 (Fig. 4c) and option 1 (Fig. 4b), in each switching cycle to generate  $V_{sw}=2V_{out}$ . In this way, the input charge is redistributed to the load every two switching cycles.

To implement this modified control, simple logic conditions can be added to generate alternative PWM signals from second and third levels of multilevel carrier signals in Fig. 3 for  $Sw_{5,7}$ and  $Sw_{8,10}$ . These conditions can be active for the full line cycle without changing the basic operation of the converter. Fig. 5a depicts the simplified logical diagram for the modified operation.

To generate these control signals with a smooth transition between different regions in a more practical implementation in micro-controller, carrier signals can be modified as in Fig. 5b, where the second and third carrier signal levels are implemented with two 180° phase-shifted PWM signals with magnitudes from 0 to  ${}^{2V_M}/{}_3$ . In this way, at least once in every two switching periods, C<sub>1</sub> is also placed in parallel to C<sub>2</sub> and C<sub>2</sub> is placed in parallel to C<sub>out</sub>, which is tightly regulated. This operation makes sure the flying capacitors closely track the regulated output voltage  $V_{out}$  as frequently as every other switching cycle.

It is worth noting that, this over-voltage problem does not come into the scene during regions 1 and 2 as charge redistribution to  $C_{out}$  and  $V_{out}$  happens once in every switching period, keeping an equal voltage for all the capacitors,  $V_{C_1} = V_{C_2} = V_{C_{out}} = V_{out}$ . Also, the increased voltage for  $C_1$  in this converter is different than the imbalance problem in FCML converters. The resultant voltage variation in this converter is at line frequency, does not depend on small timing mismatches [11], and can be calculated quite precisely with existing models.

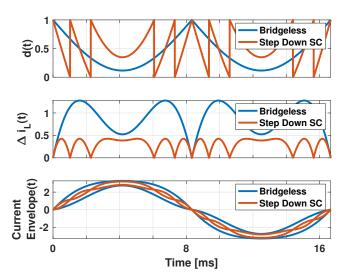

# C. Advantage of the Proposed Converter: Reduced Inductor Current Ripple

With two flying capacitors and an output capacitor, this converter can generate seven levels for V<sub>xy</sub> node voltage. As a result, in a major portion of the line cycle, the inductor is charged and discharged by a smaller amount of voltage compared to a bridge-less or totem pole PFC converter. Particularly, in region 1, the inductor is switched to either input voltage or Vout which is smaller than Vm. In region 2, the inductor voltages are |V<sub>in</sub>|-V<sub>out</sub> and 2V<sub>out</sub>-|V<sub>in</sub>|, while in region 3, they are |Vin|-2Vout and 3Vout-|Vin|. Using the inductor voltage information, the current ripple of the stepdown PFC converter is calculated and compared with a bridgeless/totem-pole PFC converter at the same power and operating point in Fig. 6. It can be observed that the new step-down PFC converter maintains smaller current ripples and thus, a narrower envelope of the inductor current throughout the operation. Hence, one can also predict a superior THD performance in the new converter compared with a bridge-less/totem-pole PFC converter at the same operating condition.

# D. Advantage of the Proposed PFC Converter: DC-Link Filtering with Distributed Low-Voltage Capacitors

In any AC-DC or DC-AC application, the choice of total DC link capacitance depends on the line frequency, maximum

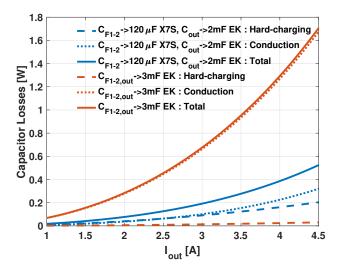

Fig. 7: Capacitor loss comparison between ceramic and electrolytic (EK) flying capacitors

Fig. 8: Controller with sensing circuits

power, and maximum allowed voltage ripple. The amount of capacitance is typically very large considering large output power and low line frequency. The presented step-down PFC converter also falls in this general category. However, different from conventional PFC converters, this converter carries out the DC-link filtering function at the low-output voltage levels. More importantly, the switched-capacitor operation with efficient charge redistribution, described in subsection II-B, allows all flying capacitors and output capacitor to participate as DC-Link capacitors. A key benefit here is that this allows the large DC-Link capacitance to be distributed among the flying capacitors with no difference in energy buffering performance. As an additional benefit, large values of flying capacitors minimize their switching-frequency ripple and hard charging loss to improve overall efficiency. The low output voltage rating requirement also enables the selection of higher-density capacitors to reduce overall implementation size and increase the system power density.

As a design aspect, one needs to select between electrolytic and ceramic capacitors for the converter. The design can be made electrolytic-free by using ceramic capacitors either with or without methods to enhance the energy buffering capability of the capacitors, for example, using series stacked energy buffer [12] or stacked switched capacitor buffer [13]. While there are certain benefits in an electrolytic-free implementation, the main drawback associated with using only ceramic capacitors for both flying and output capacitors is that they are more expensive and relatively lower energy density compared with electrolytic capacitors.

As a proof of concept, in this work, we have used electrolytic capacitors for large energy buffering capability owing to their higher capacitance density and for a relatively simpler implementation. However, as these capacitors have high ESRs, using them for flying capacitors would cause excessive conduction loss. Figure 7 shows an analytical comparison of capacitor conduction and hard-charging losses between the two cases: 1) small ceramic capacitors (X7S) are used for the flying capacitors and high-density electrolytic (EK) capacitors for the output filtering, and 2) all capacitors are electrolytic. The result is clear that the first case exhibits significantly smaller losses comparing to the other one that even has a smaller total capacitance. Following the analysis, the converter implementation in this paper, presented in Section IV-A, utilize a combination of ceramic and electrolytic capacitors for flying capacitors and output capacitors, respectively.

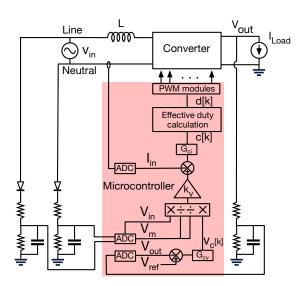

#### E. Control and Sensing Circuits

The traditional feed-forward average current mode control for the PFC boost converter has been employed to control this new converter [6]. Figure 8 illustrates the block diagram of the control procedure in a micro-controller. Small-signal model analysis of the converter's input current response and output voltage indicates the converter behaves the same way as multi-level converters and standard PFC boost converters [14]. Thus, the long existing and well adopted knowledge for the control of a PFC boost converter can readily be used to design the voltage compensator,  $G_{cv}$  and current compensator,  $G_{ci}$ . Detailed steps for this design can also be found in [6]. Delay associated poles from the micro-controller have also been considered to properly design the compensators [15].

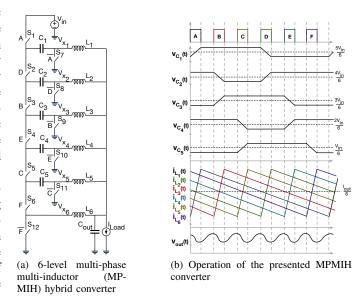

#### III. MULTI-PHASE MULTI-INDUCTOR HYBRID CONVERTER

Recently, the last stage converter for 48V-to-1V conversion has received a lot of interest in industry and academic research with remarkable implementations using both isolated [16], [17] and non-isolated architectures [18]. In this work, we utilize a member of the multi-inductor hybrid (MIH) converter family [19]–[23], a 6-level converter extension of the previously demonstrated DP-MIH converter reported in [23]. The additional inductors and interleaved phases are extended to support larger output currents compared with prior works.

Fig. 9: 6-level multi-phase multi-inductor (MP-MIH) hybrid converter and its operation with AD-BE-CF phase sequence

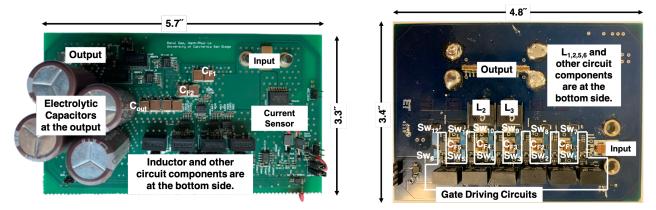

(a) Step-down PFC multi-level AC-DC converter

(b) 6-level MP-MIH DC-DC Converter using GaN FETs

Fig. 10: Two converter prototypes of the 110VAC-to-1VDC power delivery architecture

TABLE I: Components used in PFC step down converter

| Components             | Part Number             |

|------------------------|-------------------------|

| Sw <sub>1,3</sub>      | SBR10U200P5DICT-ND      |

| Sw <sub>2,4</sub>      | BSC500N20NS3GATMA1CT-ND |

| Sw <sub>5,7,8,10</sub> | BSC123N08NS3GATMA1      |

| Sw <sub>6,9</sub>      | SBRT20M80SP5-13         |

| C <sub>1,2</sub>       | 8xC5750X7S2A156M250KB   |

| C <sub>out</sub>       | 8xC5750X7S2A156M250KB+  |

|                        | 4xEKYB101ELL102MM40S    |

| L                      | IHLP6767GZER470M11      |

| Gate driver            | UCC5350MCDR             |

| Current Sensor         | ACS716KLATR-6BB-NL-T    |

TABLE II: Components used in MPMIH converter

| Components         | Part Number            |

|--------------------|------------------------|

| Sw <sub>1-6</sub>  | 2xEPC2015c             |

| Sw <sub>7-12</sub> | 2xEPC2023              |

| C <sub>1-5</sub>   | 4xCGA8M3X7S2A335M200KB |

| L <sub>1-6</sub>   | XAL1030-561ME          |

| Gate Driver        | LMG1210                |

# A. Multi Inductor Converter with Multi-Phase Operation

The 6-level MP-MIH converter is depicted in Fig. 9a. It has twelve switches  $S_{1-12}$ , five flying capacitors  $C_{1-5}$  and six inductors  $L_{1-6}$ . The input switched-capacitor (SC) network divides the input voltages by 6 times to feed into the Buck-like output filter inductors that, in turn, synchronously soft-charge and soft-discharge the flying capacitors. The high-side six switches  $S_{1-6}$  are controlled by six multi-phase pulse width modulated (PWM) signals, A-F with duty cycle, D, while the ground-connected freewheeling switches  $S_{7-12}$  are controlled by six complementary signals,  $\overline{A}$ - $\overline{F}$ , respectively. Accordingly, the output voltage and flying capacitor  $C_i$  voltages can be represented by  $V_{out} = \frac{DV_{in}}{6}$  and  $V_{C_i} = \frac{6-i}{6}V_{in}$  where i =1-5. The key constraint in the converter operation is that no two consecutive signals controlling two consecutive high-side switches in  $S_{1-6}$  can overlap. Following this constraint, the converter can support an operation of two to six interleaving phases with the six inductors of the six-level converter. While a maximum number of phases yields advantages in output voltage ripple and transient response as well as switching loss reduction, it also limits maximum duty cycle and thus maximum output voltage. For example, for six phases are nonoverlapped and evenly distributed with 60° phase shift and A-F are arranged for the switches Sw<sub>1-6</sub> sequentially, each of the phases A-E has a maximum duty cycle of 1/6, limiting the maximum output voltage to  $V_{in}/36$ . However, it is also possible to arrange the phases in a different, non-sequential method to allow a larger maximum duty cycle while still satisfying the requirement of no overlap in consecutive phases. Figure 9b depicts an example operation where steady-state operation of the MP-MIH converter using this strategy. The six non-overlapped phases, in the order of A to F, are limited to 3/6, 2/6, 2/6, 3/6, 3/6, and 3/6 respectively. This arrangement allows a maximum output voltage  $V_{in}/18$  while still obtaining the benefits of a 6-phase interleaving operation with equal duty cycles. When a maximum output voltage is prioritized, the converter operation can be changed to 2-phase interleaving to reach an output voltage of  $V_{in}/12$ .

# **IV. EXPERIMENTAL RESULTS**

The two-stage 110VAC-to-1VDC power delivery architecture has been implemented using two converter prototypes, shown in Fig. 10a and 10b. Key components for the converters are listed in Table I and II. These converters have been tested separately and in combination to demonstrate the full structure.

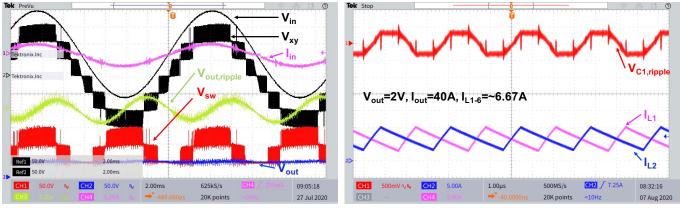

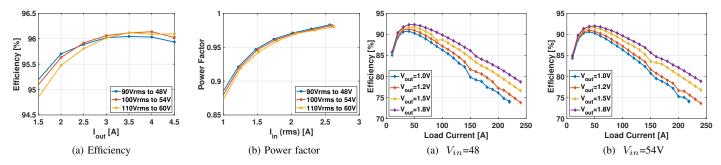

# A. Step-down PFC Converter

Figure 11a shows the key waveforms of the converter at 90VAC to 48V/4A operation. It can be seen that the input current follows the input voltage, verifying the key PFC operation. The performance of the converter is shown in Fig. 13 in terms of efficiency and power factor. The converter maintains higher than 96% efficiency for a wide range of operations and more than 95% for almost all operating points. As shown in Fig. 13b, the converter achieve a power factor of 0.98 at 2.6 A effective input current. The power factor goes down at lower input current, i.e. lower output power, because of noise and harmonics caused by multi-level switching operations that

(a) Steady state waveforms at 90Vrms to 48V/4A operation

(b) Experimental waveforms ,  $I_{L1},\,I_{L_2}$  and  $V_{C1}$  of MPMIH converter for 48V to 2V/40A conversion at 300kHz with AD-BE-CF phase sequence

Fig. 11: Steady-state operation of Step-down PFC converter and the MPMIH converter

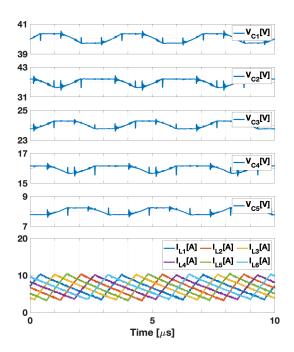

Fig. 12: Measured capacitor and inductor waveforms of the MP-MIH converter prototype for 48V to 2V/40A operation

couple to and reduce the accuracy of the current sensor and the current regulation loop. The power density of this converter at the full power is 73W/in<sup>3</sup>, including all the components including output electrolytic capacitors.

#### B. MP-MIH Converter

Figure 12 shows the key waveforms of the MPMIH converter in a 48V to 2V/40A operation example. Using a phase sequence selection presented in Fig. 9, the converter's output current was a 6-phase interleaved combination of inductor currents. The converter can also support up to ~4 VDC output. The standalone performance of this converter is presented in Fig. 14. At 48V-to-1V operation this converter achieved a peak efficiency of 90.75% at 40A load current, whereas, 92.31% was acheived for a 48V-to-1.8V conversion and at 50A output

current. The converter was tested to a maximum load current of 220 A at 1V and 240 A at 1.2-1.8V. Considering the components in the power flow path, this converter achieved current density of 1.03 kA/in<sup>3</sup> for 1V and 1.123 kA/in<sup>3</sup> for other output voltages which translates into 1.03 kW/in<sup>3</sup> and 2.02 kW/in<sup>3</sup> peak power densities for 1V and 1.8V output voltages, respectively. Similar experiments have also been carried out for 54V input voltage. At 54V input voltage, this converter achieved peak efficiency of 90.6% and 92% for 1V and 1.8V output voltage, respectively.

# C. Full System Verification

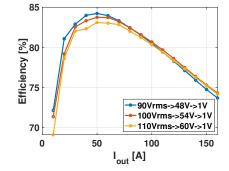

The MP-MIH converter was connected to the step-down PFC converter's output to complete the full power delivery system that bridges an AC distribution voltage to core DC voltages. Figure 15 shows the operations of the full system in line and load transients. The waveforms of input inductor current  $(I_{in})$ , output current  $(\frac{I_{out}}{4})$ , switching voltage  $(V_{sw})$ , and output voltage  $(V_{out})$ , illustrate stable operations and regulations of the converter and output voltage when the converter is exposed to a 40 Vrms line voltage step (Fig. 15a) and a 50A load step ((Fig. 15b). The first-stage step-down PFC hybrid converter can provide fast response toward big line transients thanks to the flying capacitors capable of changing multiple levels, while remaining variations at the output of the first stage are managed by the second stage regulation. The seamless duty cycle control from the second stage also takes care of the high load current transient at the final output. The overall efficiency of the system is shown in Fig. 16. For 110VAC-to-1VDC operation, the overall efficiency peak is 84.1%. The peak output current when testing the full system is limited to 160A because of a non-fundamental limit in the design of the first-stage AC-DC converter which has an output current under 4.5A.

For comparison, a conventional power delivery architecture using 4 conversion stages for the same application would require all stages to individually achieve, on average, an efficiency of 95.8% to reach an equivalent performance of this proposed two-stage architecture. Considering the full

Fig. 13: Performance of the step-down PFC Converter

50A to 100A load transient.

(a) Operation at 1V/50A for a 50Vrms to 90Vrms line transient

Fig. 15: Measured waveforms of the complete two-stage architecture for line and load transients

conversion of from 110 VAC to 1 VDC, to the authors' best knowledge this has not been demonstrated.

# V. CONCLUSION

In this work, we have successfully demonstrated the first two-stage architecture to directly convert AC distribution voltage to the core voltages that can be applied to power delivery in data centers and telecommunication systems. The demonstration includes a new switched-capacitor multi-level stepdown PFC converter and a 6-level switched-capacitor-based multi-phase multi-inductor hybrid (MPMIH) converter. The operation of the step-down PFC converter was discussed with control mechanisms for output voltage and input current regulations. A simple method of charge redistribution for flying capacitor voltage balancing at the carrier switching frequency was also provided. In designing the MP-MIH converter, a new phase sequence has been proposed and verified in experiments for larger output voltage and current ranges. The converter designs are verified separately and together in the complete two-stage AC grid-to-Core voltage system, demonstrating a bright promise for future applications to contribute to more green and energy-efficient data centers, telecommunication, and other IT systems.

#### REFERENCES

- A. Pratt, P. Kumar, K. Bross, and T. Aldridge, "Powering Compute Platforms in High Efficiency Data Centers," Intel Corporation, Tech. Rep.

- [2] P. Yeaman, "Datacenter Power Delivery Architectures : Efficiency and Annual Operating Costs," Vicor Corporation, Tech. Rep.

- [3] Cisco and/or its affiliates, "Cisco Global Cloud Index: Forecast and Methodology, 2015–2020," Tech. Rep., 2016.

(b) Operation at 1V from 90Vrms input voltage for a 50A to 100A load transient

Fig. 16: Efficiency of the full AC Grid-to-Core voltages system

- [4] R. Moller, "Ericsson Mobility Report November 2017," Ericsson, Tech. Rep.

- [5] D. M. Mitchell, "AC-DC Converter having an improved power factor," US Patent US4412277A, Oct., 1983.

- [6] R. W. Erickson and D. Maksimović, "Pulse-width modulated rectifiers," in *Fundamentals of Power Electronics*, pp. 867–930. Springer International Publishing, 2020.

- [7] Y. Hinago and H. Koizumi, "A Switched-Capacitor Inverter Using Series/Parallel Conversion With Inductive Load," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 2, pp. 878–887, Feb. 2012.

- [8] M. N. H. Khan, M. Forouzesh, Y. P. Siwakoti, L. Li, and F. Blaabjerg, "Switched Capacitor Integrated (2n + 1)-Level Step-Up Single-Phase Inverter," *IEEE Transactions on Power Electronics*, vol. 35, no. 8, pp. 8248–8260, Aug. 2020.

- [9] R. Barzegarkhoo, Y. P. Siwakoti, and F. Blaabjerg, "A New Switched-Capacitor Five-Level Inverter Suitable for Transformerless Grid-Connected Applications," *IEEE Transactions on Power Electronics*, vol. 35, no. 8, pp. 8140–8153, Aug. 2020.

- [10] G.-S. Seo and H.-P. Le, "S-Hybrid Step-Down DC-DC Converter—Analysis of Operation and Design Considerations," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 1, pp. 265–275, Jan. 2020.

- [11] R. Das, J. Celikovic, S. Abedinpour, M. Mercer, D. Maksimovic, and H.-P. Le, "Demystifying Capacitor Voltages and Inductor Currents in Hybrid Converters," in 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), DOI 10.1109/COMPEL.2019.8769722, pp. 1–8, Jun. 2019.

- [12] S. Qin, Y. Lei, C. Barth, W.-C. Liu, and R. C. N. Pilawa-Podgurski, "A High Power Density Series-Stacked Energy Buffer for Power Pulsation Decoupling in Single-Phase Converters," *IEEE Transactions on Power Electronics*, vol. 32, no. 6, pp. 4905–4924, Jun. 2017.

- [13] S. Pervaiz, A. Kumar, and K. K. Afridi, "A Compact Electrolytic-Free Two-Stage Universal Input Offline LED Driver With Volume-Optimized SSC Energy Buffer," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 3, pp. 1116–1130, Sep. 2018.

- [14] R. W. Erickson and D. Maksimović, "Current-programmed control," in *Fundamentals of Power Electronics*, pp. 725–804. Springer International Publishing, 2020.

- [15] L. Corradini, D. Maksimović, P. Mattavelli, and R. Zane, *Digital Control of High-Frequency Switched-Mode Power Converters: Corradini/Digital Control of High-Frequency Switched-Mode Power Converters.* Hoboken, NJ, USA: John Wiley & Sons, Inc, Jun. 2015.

Fig. 14: Efficiency of the MP-MIH converter

- [16] S. Khatua, D. Kastha, and S. Kapat, "A New Single-Stage 48-V-Input VRM Topology Using an Isolated Stacked Half-Bridge Converter," *IEEE Transactions on Power Electronics*, vol. 35, no. 11, pp. 11976–11987, Nov. 2020.

- [17] A. Kumar, S. Pervaiz, and K. K. Afridi, "High-Performance Single-Stage Isolated 48V-to-1.8V Point-of-Load Converter Utilizing Impedance Control Network and Distributed Transformer," in 2018 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 3838–3843, Sep. 2018.

- [18] M. H. Ahmed, C. Fei, F. C. Lee, and Q. Li, "48-V Voltage Regulator Module With PCB Winding Matrix Transformer for Future Data Centers," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 12, pp. 9302–9310, Dec. 2017.

- [19] K. Abe, K. Nishijima, K. Harada, T. Nakano, T. Nabeshima, and T. Sato, "A Novel Three-Phase Buck Converter with Bootstrap Driver Circuit," in 2007 IEEE Power Electronics Specialists Conference, pp. 1864–1871, Jun. 2007.

- [20] G.-S. Seo, R. Das, and H.-P. Le, "Dual Inductor Hybrid Converter for Point-of-Load Voltage Regulator Modules," *IEEE Transactions on Industry Applications*, vol. 56, no. 1, pp. 367–377, Jan. 2020.

- [21] R. Das, G.-S. Seo, and H.-P. Le, "Analysis of Dual-Inductor Hybrid Converters for Extreme Conversion Ratios," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, DOI 10.1109/JESTPE.2020.2985116, pp. 1–1, 2020.

- [22] R. Das, G. Seo, D. Maksimovic, and H.-P. Le, "An 80-W 94.6%-Efficient Multi-Phase Multi-Inductor Hybrid Converter," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 25–29, Mar. 2019.

- [23] R. Das and H.-P. Le, "A Regulated 48V-to-1V/100A 90.9%-Efficient Hybrid Converter for POL Applications in Data Centers and Telecommunication Systems," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1997–2001, Mar. 2019.

**Ratul Das** (S'15) received the B.Sc. and M.Sc. degrees in Electrical and Electronic Engineering from the Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh, in 2015 and 2017, respectively. He worked in the Integrated Power Electronics and Energy Efficient Systems (iPower3Es) group at the Colorado Power Electronics Center (CoPEC), University of Colorado at Boulder from 2017 to 2019 as a graduate student researcher. Currently, he is focusing on his journey towards the PhD

degree with the iPower3Es group at the University of California San Diego, La Jolla, CA. Mr. Das was the recipient of a Gold Outstanding Graduate Student Researcher Award 2019 from the ECEE department of University of Colorado Boulder, a Best Paper Award at IEEE COMPEL 2019 and a second prize award in IEEE ECCE 2019 student project demonstrations.

Hanh-Phuc Le (M'13-SM'19) received the B.S. degree from the Hanoi University of Science and Technology (HUST), Hanoi, Vietnam, in 2004, the M.S. degree from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2006, and the PhD degree from the University of California at Berkeley, Berkeley, CA, USA, in 2013, all in Electrical Engineering. He is currently an Assistant Professor at the Electrical and Computer Engineering at San

Diego (UCSD), La Jolla, CA, USA. He was also with the University of Colorado at Boulder, Boulder, CO, USA, from 2016 to 2019. Dr. Le was a recipient of the 2012-2013 IEEE SSCS Pre-Doctoral Achievement Award, and the 2013 Sevin Rosen Funds Award for Innovation at University of California at Berkeley. He is currently the Chair of the Technical Committee on Power Conversion Systems and Components in the IEEE Power Electronics Society (IEEE PELS TC2).