### A Novel Hybrid RF-DC Converter using CMOS n-Well Process

Muneer Al Absi $^{\rm 1}$

#### $^{1}\mathrm{KFUPM}$

October 30, 2023

#### Abstract

It is well known that CMOS Cross-coupled Differential Drive (CCDD) is the commonly used approach in the design of RF-DC converters. However, multistage designs are usually used to produce higher DC output voltage. This in turn will lead to using the twin-well CMOS process for fabrication since the NMOS source will be at higher potential in the next and consequent stages. The twin-well process technology is expensive compared to the n-well process. On the other hand, the DC output of these designs will saturate when higher voltage is required using multistage. This brief presents a new CMOS n-well process RF-DC converter. The design is hybrid in which the first stage is designed using CCDD since the NMOS source is grounded and the second and consequent stages are designed using only PMOS transistors. The functionality of the proposed design is confirmed using CADENCE in 0.18 $\mu$ m TSMC CMOS technology. Simulation results show that the design is working properly and achieves linear DC output voltage with the number of stages and an input power range of 33dB for PCE >20%.

# A Novel Hybrid RF-DC Converter using CMOS n-Well Process

## (March 2023)

**Munir A. Al-Absi<sup>1,2</sup>, IEEE, Senior member and Abdulaziz. Alkhulaifi<sup>1</sup>** <sup>1</sup>King Fahd University of Petroleum & Minerals , Dhahran Saudi Arabia <sup>2</sup>Center for SML, King Fahd University of Petroleum & Minerals, Dhahran, Saudi Arabia

Corresponding author: Munir A. Al-Absi (e-mail: mkulaib@ kfupm.edu.sa).

This work is supported by King Fahd University of Petroleum and Minerals, Project No. SB201018.

**ABSTRACT** It is well known that CMOS Cross-coupled Differential Drive (CCDD) is the commonly used approach in the design of RF-DC converters. However, multistage designs are usually used to produce higher DC output voltage. This in turn will lead to using the twin-well CMOS process for fabrication since the NMOS source will be at higher potential in the next and consequent stages. The twin-well process technology is expensive compared to the n-well process. On the other hand, the DC output of these designs will saturate when higher voltage is required using multistage. This brief presents a new CMOS n-well process RF-DC converter. The design is hybrid in which the first stage is designed using CCDD since the NMOS source is grounded and the second and consequent stages are designed using only PMOS transistors. The functionality of the proposed design is confirmed using properly and achieves linear DC output voltage with the number of stages and an input power range of 33dB for PCE >20%.

**INDEX TERMS** Energy harvesting, Efficiency, Dynamic range, Rectifier.

#### I. INTRODUCTION

CMOS rectifiers are the core block in RF-DC converter. There anv are two prominent topologies: Cross-Coupled Differential-Drive (CCDD) and Dickson rectifiers in CMOS technology [1-10]. Most of the designs reported in the literature use the CCDD approach. These designs will be fabricated in a twin well CMOS process whenever multistage cells are required to have a higher DC output voltage. This process is expensive compared to the n-well process.

This work presents a new design in which only an n-well process is used. The first stage will be a normal CCDD (consists of NMOS and PMOS transistors). In this stage the source and the bulk of the NMOS are connected to ground. The consequent stages are designed using PMOS only and connected in a different way. The rest of the paper is organized as follows: The proposed design is presented in section II. Section III reports the simulation results. The paper conclusion is presented in section IV.

#### II. PROPOSED DESIGN

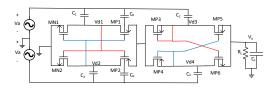

The proposed RF-DC converter is shown in Figure 1. In this design, it is assumed that the RF input is applied to a matching network and then to a balun. The balun acts like a center-tape transformer with two 180° phase shift output as shown in Figure 1.

FIGURE 1. The circuit diagram of the proposed hybrid RF-DC converter.

1

The first stage is formed using the well-known CCDD because the NMOS has lower threshold. The body terminal of the PMOS is connected to either RF+ or RF- signal via coupling capacitors to control the threshold voltage during the ON and the OFF states.

The second and the consequent stages are designed using PMOS only and connected in a different way as shown in Figure 1. Hence an n-well process instead of the twin-well is used to fabricate these types of rectifiers. Consequently, less area and less cost will be the main achievement. In addition, the DC output increases almost linearly with the number of stages and can produce higher output voltage.

The rectifier operation is as follows: the first stage is normal CCDD, and during the negative half of the cycle, transistors MN1 and MP2 will be ON, and hence  $C_1$  will charge to Va-V<sub>DS1</sub> and the charge in  $C_2$  is pumped to the output. The opposite will happen in the positive half of the cycle. The same will happen for next PMOS stage where  $C_1$  will charge through MP3 and the charge in  $C_2$  will be pumped to the output via MP6

#### **III. SIMULATION RESULTS**

The proposed design is implemented in 0.18 $\mu$ m TSMC CMOS process technology and verified using Cadence Virtuoso environment. The aspect ratios of transistors are chosen for CCDD to be MN1=MN2=20 $\mu$ m/.18 $\mu$ m and MP1=MP2=100 $\mu$ m /0.18 $\mu$ m. For the second and consequent stages the size for all transistors is 20 $\mu$ m/0.18 $\mu$ m. The flying

capacitors  $C_1 = C_2 = C_b= 1pF$ , and  $C_L = 2pF$ . The frequency of the signal is 920MHz.

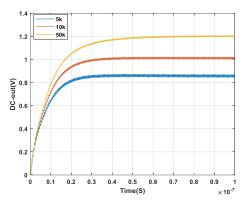

The first two hybrid stage design was simulated for different loads namely  $(5k\Omega, 10k\Omega, 50k\Omega)$ . Plots of the DC output voltages are shown in figure 2. It is clear from the figure that increasing the load will increase the output voltage. However, it was noted that increasing the load beyond  $100k\Omega$  will not make a significant increase in the output voltage.

FIGURE 2. Plots of the DC output voltage for different loads.

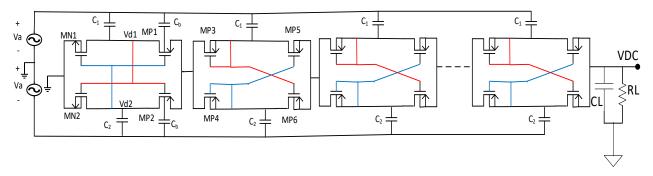

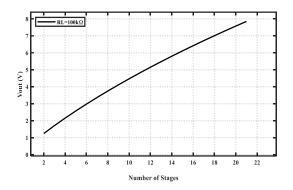

To achieve a higher DC output voltage, one can cascade the stages without adding any capacitors between stages as shown in figure 3. Plot of the simulated DC output voltage as a function of the number of stages is shown in Figure 4. It is clear from the plot that DC output increases almost linearly with the number of stages. The DC output reaches 8V when cascading 21 stage.

1

FIGURE 3. Connection for cascading stages

FIGURE 4. Plot of the output voltage vs the number of stages.

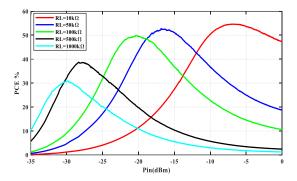

Plots of the efficiency of the rectifier for different loads are shown in figure 5. It can be seen that the PDR is 33dB.

FIGURE 5. Plots of efficiency vs the input power for different loads.

#### **IV. CONCLUSION**

A new n-well process RF-DC converter is developed. The design uses CCDD as a first stage and the next stages are all designed using PMOS transistors. The proposed design provides a linear DC output voltage with the number of stages and achieves excellent input power range for PCE >20%. We believe that there is a chance to improve the efficiency and make this hybrid design the most efficient in all aspects.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the support provided by the Deanship of Research Oversight and Coordination (IRC for smart mobility and logistics) at King Fahd University of Petroleum & Minerals (KFUPM) for funding this work through project No. SB201018

#### REFERENCES

[1] K. Kotani, A. Sasaki, and T. Ito, "High-efficiency differential-drive CMOS rectifier for UHF RFIDs," IEEE J. Solid-State Circuits, vol. 44, no. 11, pp. 3011–3018, Nov. 2009.

[2] A. K. Moghaddam et al., "A 73.9% efficiency CMOS rectifier using a lower DC feeding (LDCF) self-body-biasing technique for far-field RF energy-harvesting systems," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 64, no. 4, pp. 992–1002, Apr. 2017.

[3] J. Yi, W.-H. Ki, and C.-Y. Tsui, "Analysis and design strategy of UHF micro-power CMOS rectifiers for micro-

sensor and RFID applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 54, no. 1, pp. 153–166, Jan. 2007.

[4] A. S. Almansouri, M. H. Ouda, and K. N. Salama, "A CMOS RF-to-DC power converter with 86% efficiency and -19.2-dBm sensitivity," IEEE Trans. Microw. Theory Techn., vol. 66, no. 5, pp. 2409–2415, May 2018.

[5] M. H. Ouda, W. Khalil, and K. N. Salama, "Self-biased differential rectifier with enhanced dynamic range for wireless powering," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 64, no. 5, pp. 515–519, May 2017

[6] M. H. Ouda, W. Khalil, and K. N. Salama, "Wide-range adaptive RF-to-DC power converter for UHF RFIDs," IEEE Microw. Wireless Compon. Lett., vol. 26, no. 8, pp. 634–636, Aug. 2016

[7] S. Nagaveni, P. Kaddi, A. Khandekar, and A. Dutta, "Resistance compression dual-band differential CMOS RF energy harvester under modulated signal excitation," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 67, no. 11, pp. 4053– 4062, Nov. 2020.

[8] D. Khan, S. J. Oh, K. Shehzad, M. Basim, D. Verma, Y. G. Pu, M. Lee, K. C. Hwang, Y. Yang, and K.-Y. Lee, "An efficient reconfigurable RF-DC converter with wide input power range for RF energy harvesting," IEEE Access, vol. 8, pp. 79310–79318, 2020

[9] Z. Zeng, S. Shen, X. Zhong, X. Li, C.-Y. Tsui, A. Bermak, R. Murch, and E. Sanchez-Sinencio, "Design of subgigahertz reconfigurable RF energy harvester from -22 to 4 dBm with 99.8% peak MPPT power efficiency," IEEE J. Solid-State Circuits, vol. 54, no. 9, pp. 2601–2613, Sep. 2019.

[10] P. Saffari, A. Basaligheh, and K. Moez, "An RF-to-DC rectifier with high efficiency over wide input power range for RF energy harvesting applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 66, no. 12, pp. 4862–4875, Dec. 2019.

**MUNIR A. AL-ABSI** received the B.Sc. and M.Sc. degrees from the King Fahd University of Petroleum and Minerals (KFUPM), Dhahran, Saudi Arabia, in 1984 and 1987, respectively, and the Ph.D. degree from UMIST, U.K., in 2001. He is currently a Professor with the EE Department, KFUPM, teaching electronics and instrumentation courses. His research interests in electronics circuits and systems which include but not limited to low power analog design, impedance scaler, on, biomedical circuits, energy harvesting, and analog

impedance emulation, biomedical circuits, energy harvesting, and analog signal processing applications.

ABDULAZIZ A. AL-KHULAIFI received the B.Sc. degree from Umm Al-Qura University (UQU), Makkah, Saudi Arabia, in 2015 and received the M.Sc. degree from the King Fahd University of Petroleum and Minerals (KFUPM), Dhahran, Saudi Arabia, in 2019. During the study of M.Sc., he was a Research Assistant with the EE department, KFUPM. He is currently a Lecturer with the EE Department, KFUPM, teaching electronics courses His research interests include analog circuits using

MOS in weak inversion, impedance scalar and impedance emulation.